-

- Tronlong818

-

67 发帖0 回复467 积分

- 私信他 + 关注

前言

自著名华人物理学家高锟先生提出“光传输理论”,实用化的光纤传输产品始于1976年,经历了PDH→SDH→DWDM→ASON→MSTP的发展历程。本世纪初期,ASON/OADM技术已在通信技术当中广泛应用,逐渐发展成为以骨干网络传输为介质的ROADM技术。

图1

光通信技术具有如下特点:

(1) 信息容量大。

(2) 损耗低,可长距离传送。

(3) 抗电磁干扰能力强。

(4) 安全性能和保密性好。

(5) 重量轻,体积小,便于施工维护。

(6) 原材料来源丰富潜在价格低廉。

得益于以上特点,光通信在软件无线电、视频追踪、光电探测、定位导航、水下通信、电力设备等场合应用十分广泛。而10G光模块经历了从300Pin、XENPAK、X2、XFP的发展,最终实现了用和SFP一样的尺寸传输10G的信号,这就是SFP+。SFP凭借其小型化、低成本等优势满足了设备对光模块高密度的需求,从2002年标准推行到2010年,已经取代XFP成为10G市场主流。

创龙科技(Tronlong)的Kintex-7、Zynq-7045/7100等处理板卡已提供2/4通道SFP+光口,可实现UDP或Aurora 10G光口通信。本文将为您分享基于Kintex-7 FPGA SFP+光口的10G UDP网络通信开发案例。如需基于Kinte-7 FPGA或者ZYNQ的Aurora开发案例,欢迎与我们联系。

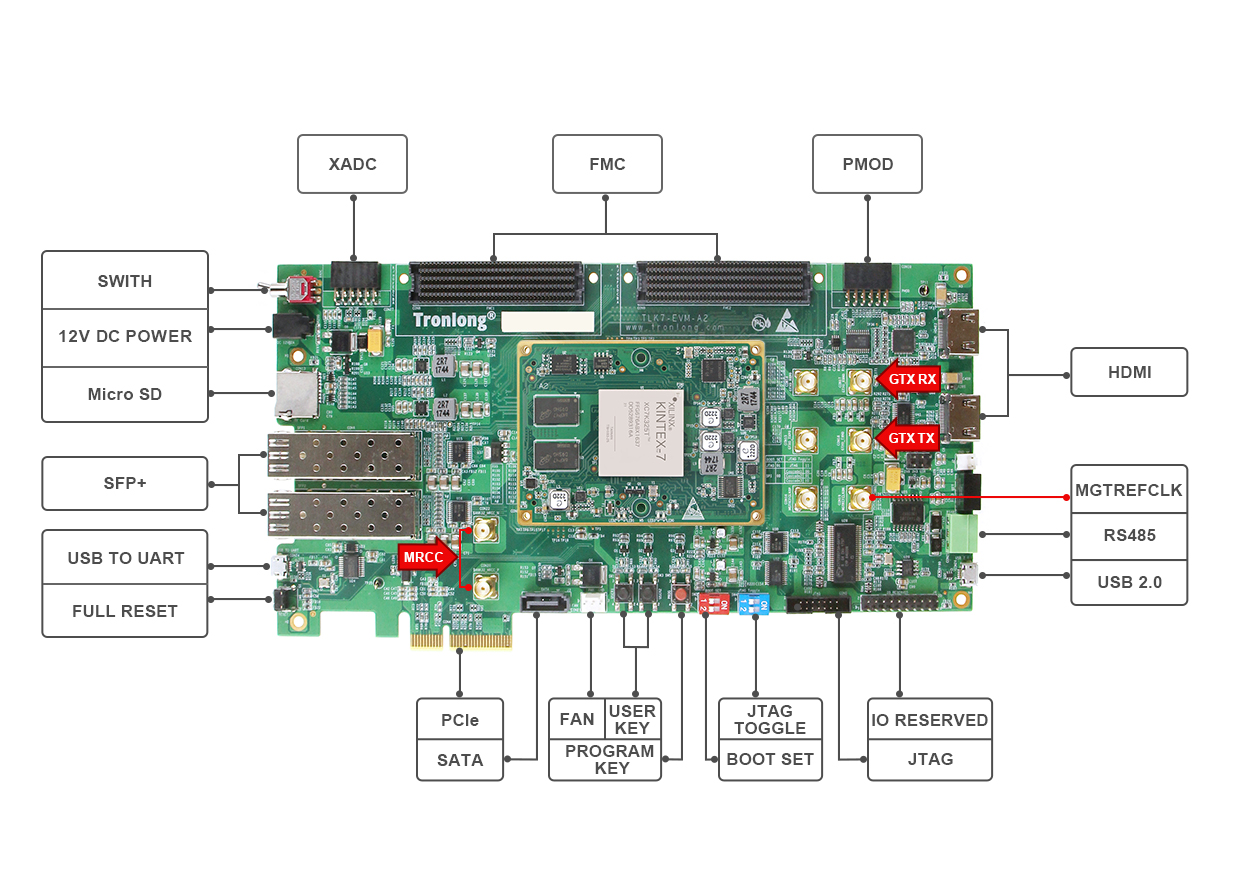

1 硬件平台

本文基于创龙科技TLK7-EVM评估板进行演示。

TLK7-EVM是一款基于Xilinx Kintex-7系列FPGA设计的高端评估板,由核心板和评估底板组成。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

评估板接口资源丰富,引出FMC、SFP+、PCIe、SATA、HDMI等接口,方便用户快速进行产品方案评估与技术预研。

图2 TLK7-EVM评估板

开发案例主要包括:

● CameraLink、SDI、HDMI、PAL视频输入/输出案例

● 高速AD(AD9613)采集 +高速DA(AD9706)输出案例

● AD9361软件无线电案例

● UDP(10G)光口通信案例

● UDP(1G)光口通信案例

● Aurora光口通信案例

● PCIe通信案例

案例源码、产品资料(用户手册、核心板硬件资料、产品规格书)可点击获取:http://site.tronlong.com/pfdownload

2 案例功能

评估板通过SFP+光口接收上位机数据后,将数据重新发送至上位机(PC),以验证基于SFP+光口的10G UDP网络通信功能。评估板作为UDP Server,上位机作为UDP Client。

图4 程序功能框图

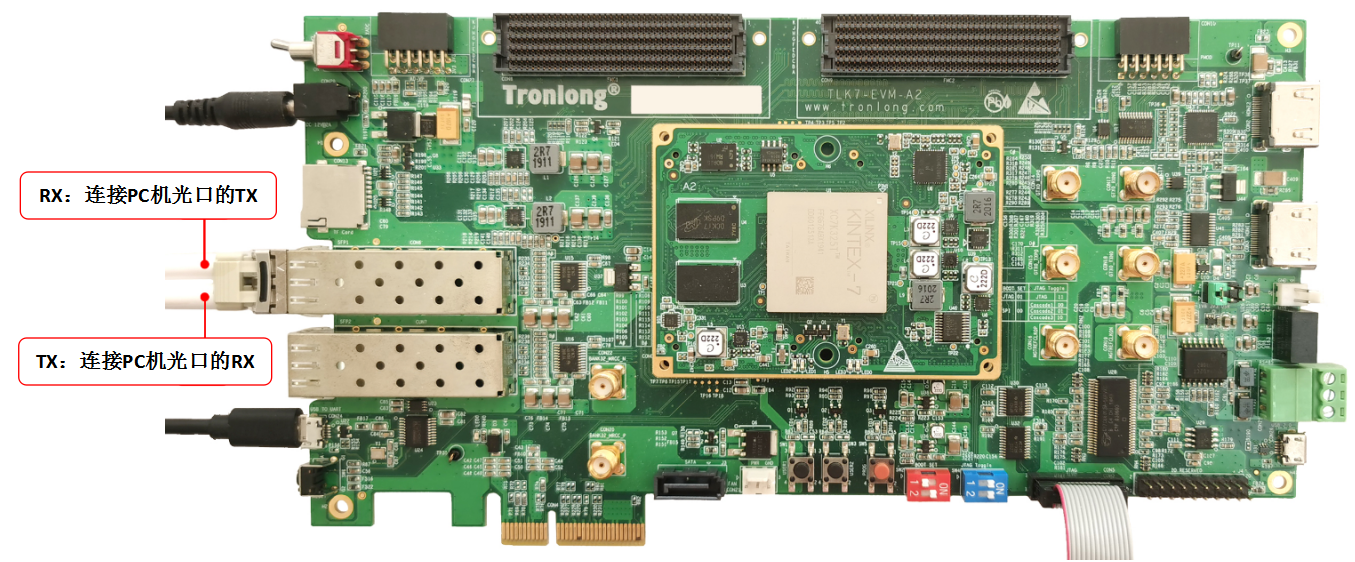

3 案例演示

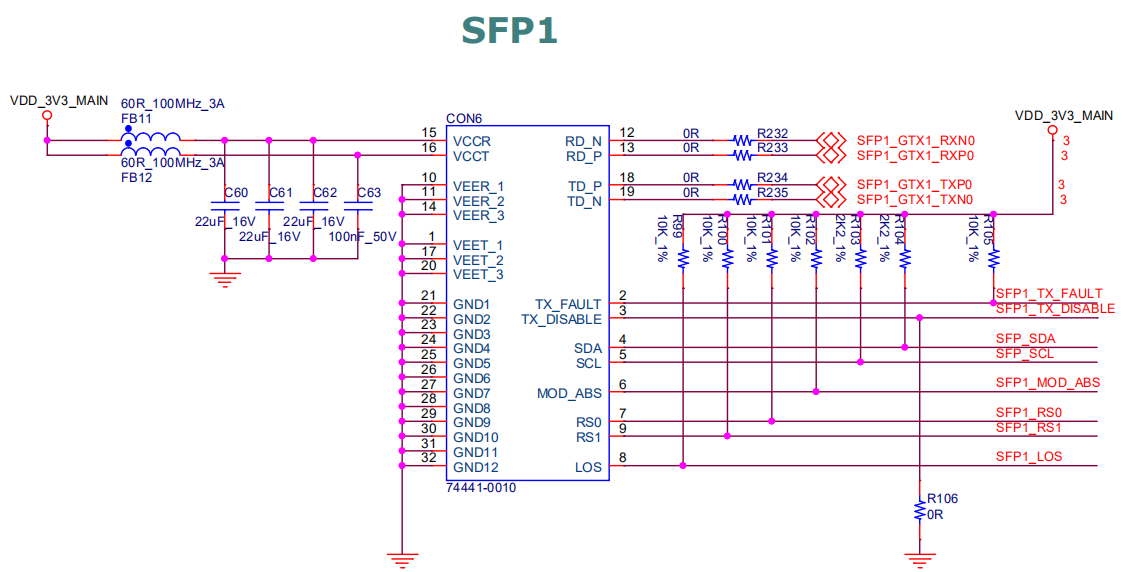

将ZBNET的万兆网卡MCX311插入PC机的PCIe插槽中,并将一个SFP+多模双纤光模块接入万兆网卡,将另一个SFP+多模双纤光模块接入评估板SFP1光口。使用两根光纤线缆分别将SFP1的RX与万兆网卡的TX相连接,SFP1的TX与万兆网卡的RX相连接。SFP1光口使用GTX Quad 116的MGTXRX_0、MGTXTX_0引脚。

图5

图6

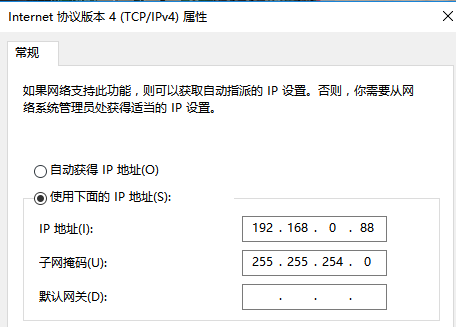

评估板IP地址已通过udp_ip_10g模块配置为192.168.0.25。请设置PC机IP地址与评估板IP地址处于同一网段。此处将PC机IP地址设置为192.168.0.88,子网掩码设为255.255.254.0。

图7

请运行程序,此时PC机将会识别网络连接状态为10Gbps。

图8

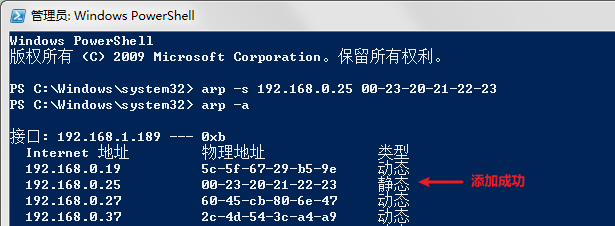

由于udp_ip_10g模块不支持ARP(Address Resolution Protocol)地址解析协议,因此需通过添加评估板IP地址和MAC地址的静态映射关系。请以管理员身份打开Windows PowerShell,并执行如下命令。

Windows#arp -s 192.168.0.25 00-23-20-21-22-23 //添加评估板IP地址和MAC地址的静态映射关系

Windows#arp -a //查看添加状态

图9

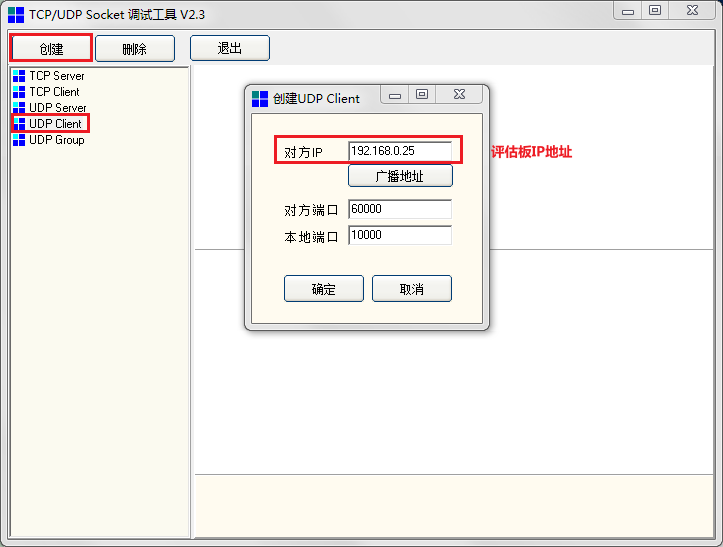

双击打开产品资料“4-软件资料\Tools\”目录下的网络调试工具SocketTool_NoAD.exe,在弹出的界面中点击“UDP Client ->创建”,在“对方IP”中输入评估板IP地址,再点击确定。

图10

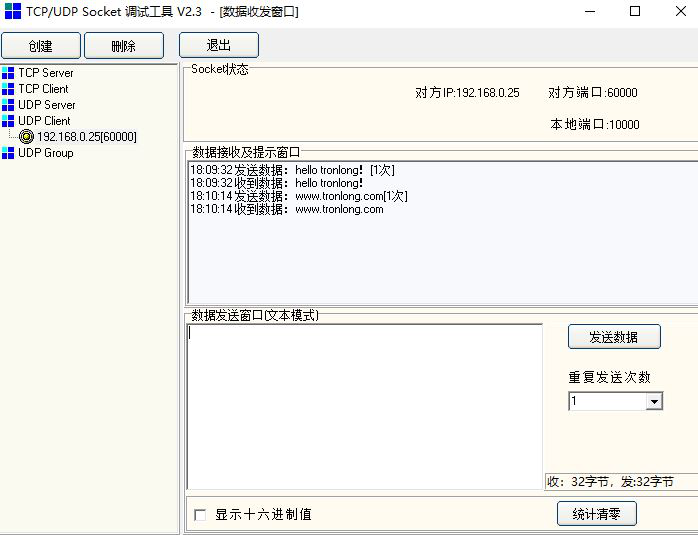

在“数据发送窗口”中输入需发送至评估板的数据,再点击“发送数据”。“数据接收及提示窗口”中将打印由PC机发送至评估板,以及由评估板发送至PC机的数据。

图11

4 模块/IP核配置

4.1 cdcm6208_spi_cfg模块

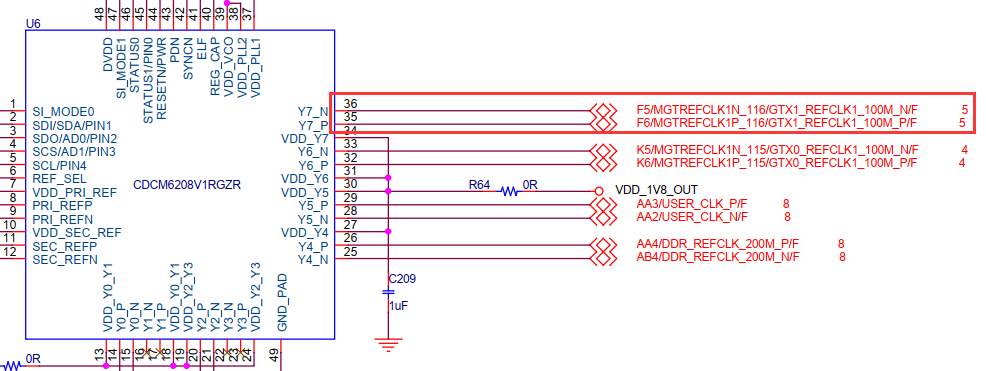

本案例使用cdcm6208_spi_cfg模块配置CDCM6208的Y7时钟管脚输出156.25MHz时钟,作为GTX Quad 116的参考时钟。

更多说明可参考clkgen_cdcm6208案例相关内容。

图12

图13

4.2 10G Ethernet PCS/PMA IP核

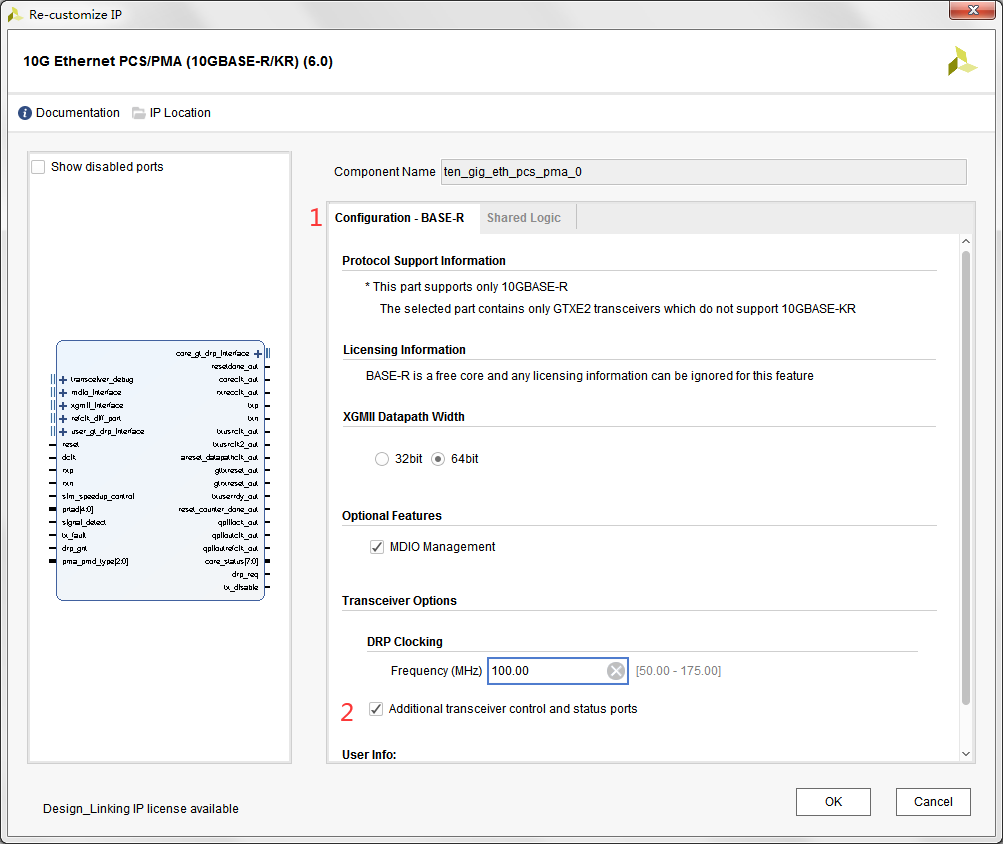

本案例使用10G Ethernet PCS/PMA IP核实现物理层(PCS与PMA)功能。

10G Ethernet PCS/PMA IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg068-ten-gig-eth-pcs-pma.pdf》,具体配置说明如下。

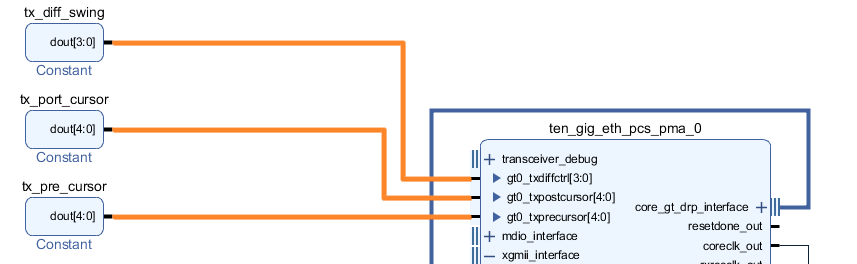

(1) 选中"Additional transceiver control and status ports",新增并设置TX Pre-Cursor、TX Post-Cursor和TX Diff Swing选项值,以提高GTX信号传输质量。其中tx_pre_cursor设置为0x15、tx_pre_cursor设置为0xA、tx_diff_swing设置为0x9。

图14

图15

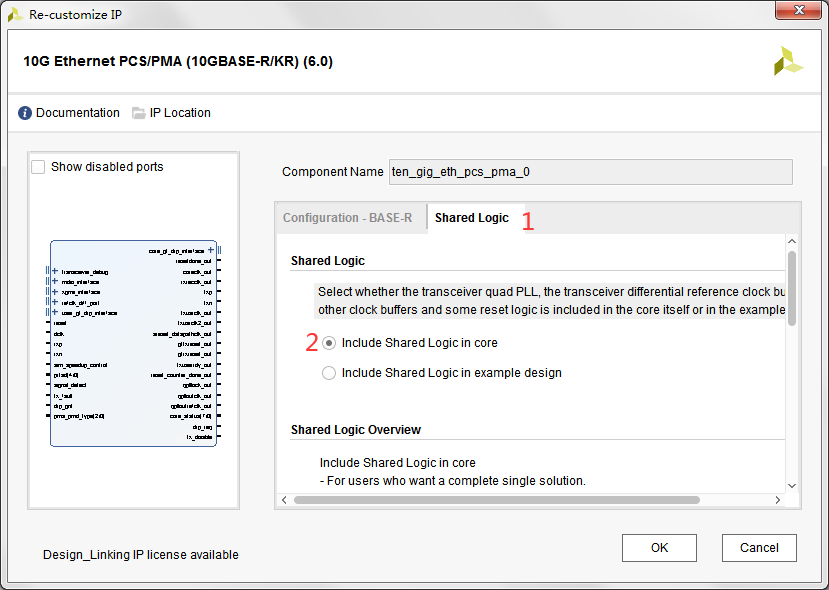

(2) 勾选Shared Logic的"Include Shared Logic in core",配置10G Ethernet PCS/PMA IP核包含共享逻辑。

图16

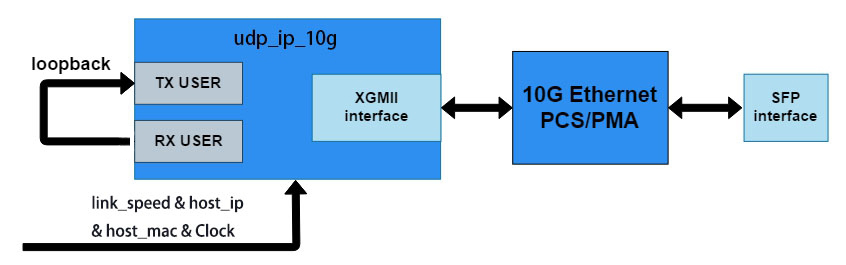

4.3 udp_ip_10g模块

本案例使用udp_ip_10g模块实现10G UDP协议栈与MAC层。

udp_ip_10g模块开发文档为产品资料“6-开发参考资料\其他参考文档\”目录下的《udp_ip_10g.pdf》。udp_ip_10g模块源码为"project\udp_10g_echo.srcs\sources_1\imports\udp_ip_10g_stack\"。

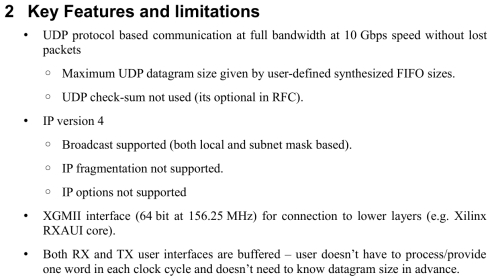

图17 udp_ip_10g模块主要特性

图18 udp_ip_10g模块逻辑框架

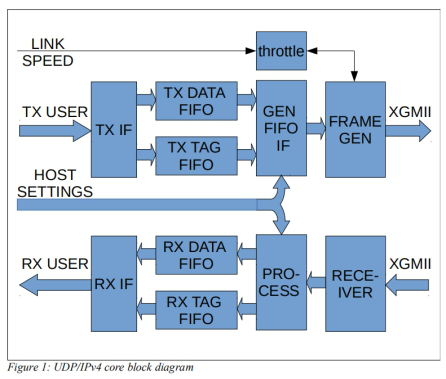

udp_ip_10g模块具体配置说明如下。

图19

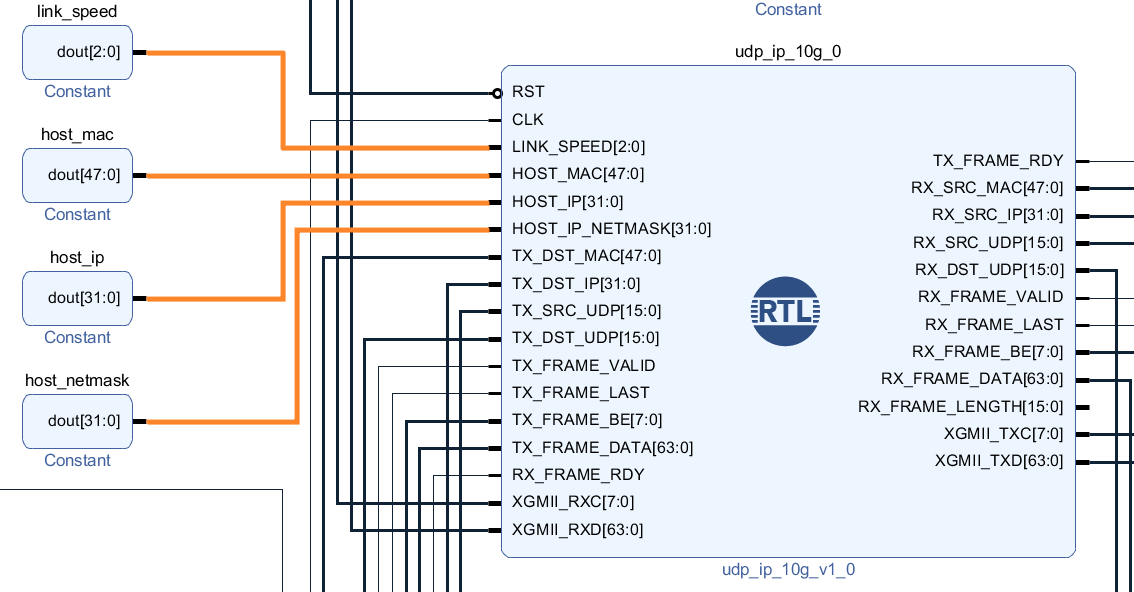

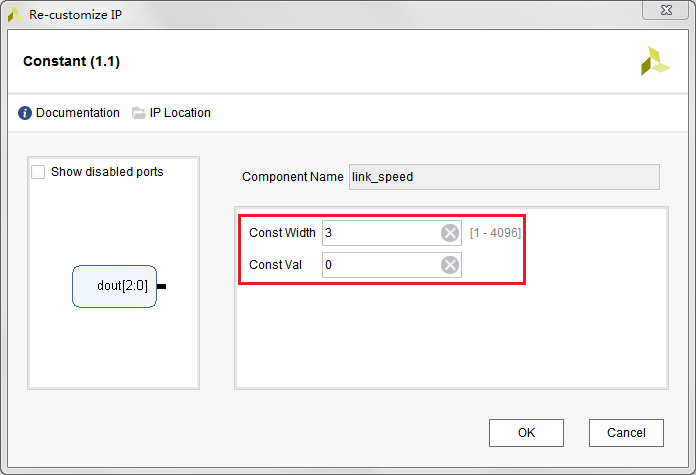

(1) 设置链路速率为10Gbps。

图20

图21

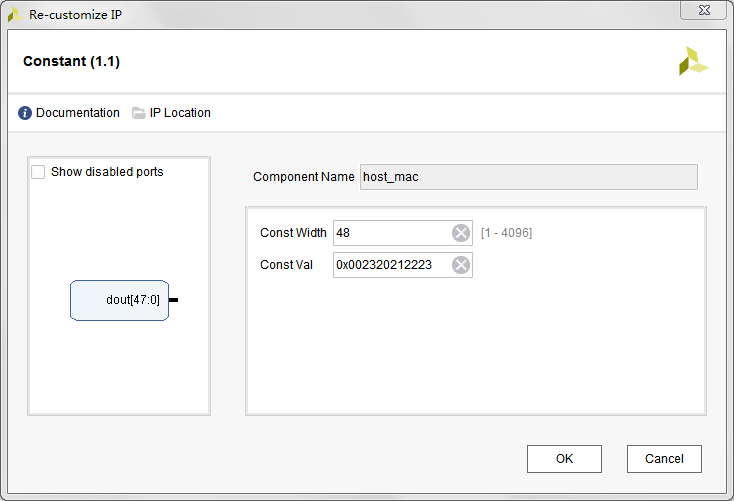

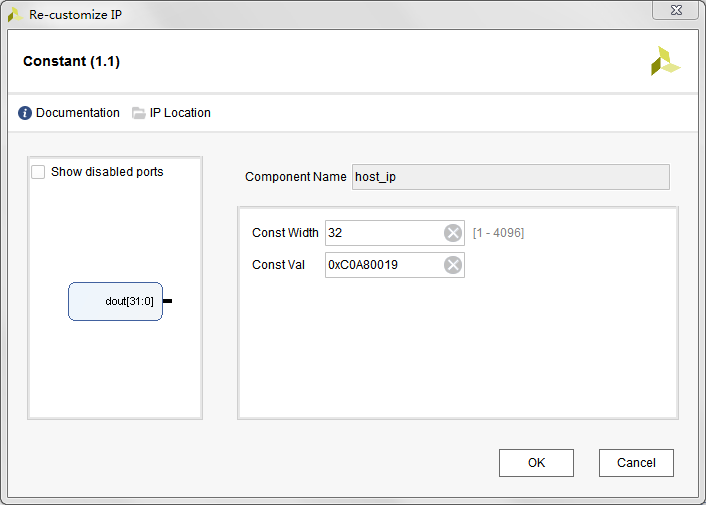

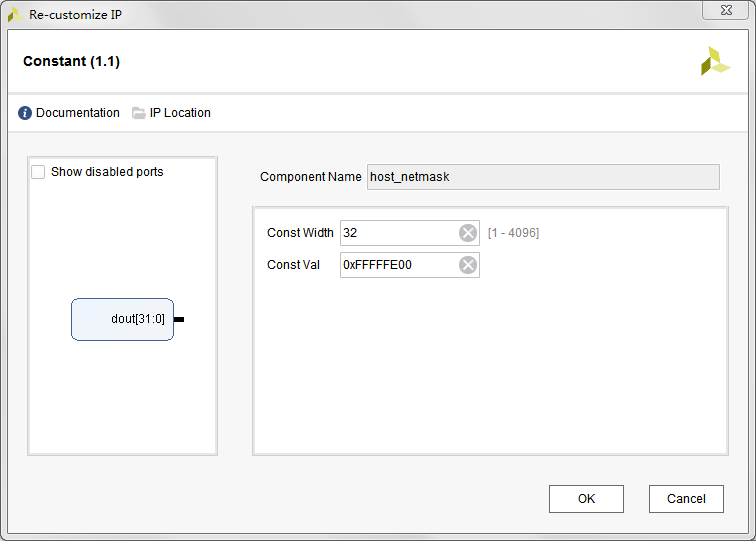

(2) 设置评估板MAC地址为00-23-20-21-22-23,IP地址为192.168.0.25,子网掩码为255.255.254.0。

图22

图23

图24

5 免费试用

扫描下方二维码,即可申请TLK7-EVM评估板进行快速评估,免费哦!

图25

6 技术交流

Kintex-7 FPGA交流:311416997、101245165

Zynq-7000交流:645235672、193393878

7 更多推荐

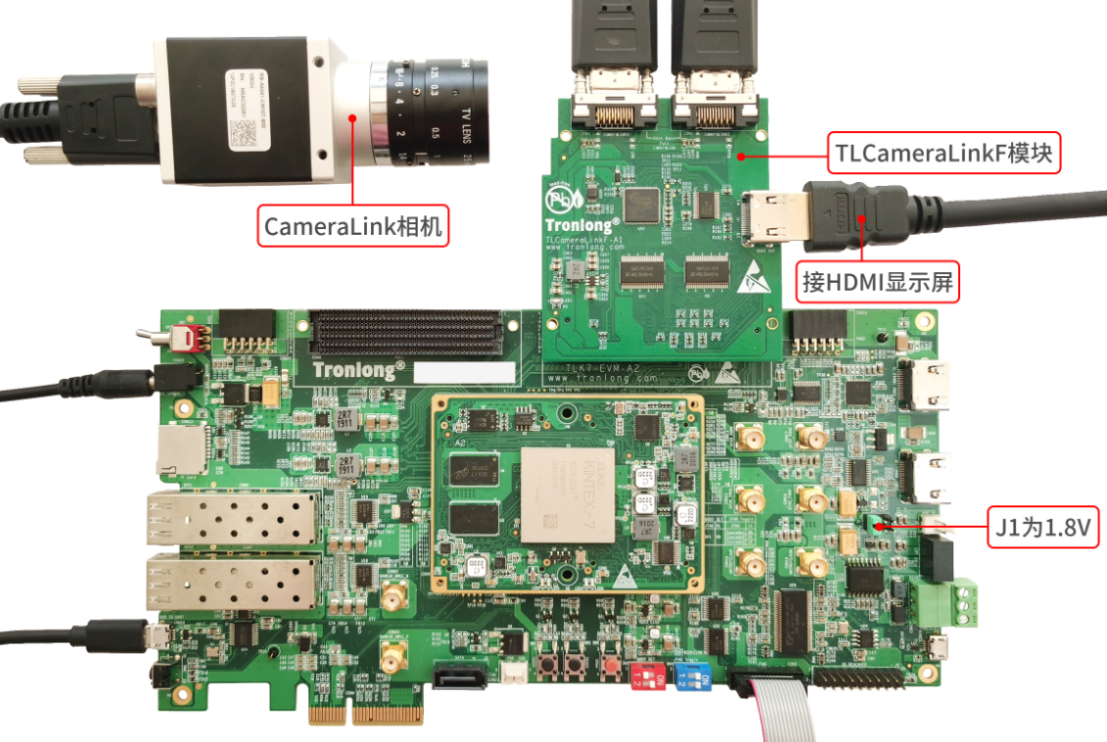

基于Kintex-7 FPGA、ZYNQ的CameraLink视频采集案例,下期为创龙科技继续为您揭晓,敬请期待。

图26

回复

回复

举报

举报

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主