1.问题:

如果pad表面铝层不平整的话,会对WB(wire bonding)有影响否?

回复:

一般pad平整度不会那么差,最可能晶圆测试过程中的针痕。有的封装厂规定针痕区域(probe mark)不能超过整个pad的25%,。面积越大Ball Shear越差,基本上到25%就加大lifting的风险。对probe mark还要求没有barrier metal或oxide exposed ,probe mark〈3X CP probe的quality。Probe mark严重的话会引起松焊,可以用ball shear进行测试验证。铝的致密度和厚薄影响也会影响wire bonding。

2.问题:

这个红圈里面的细纹是crack?还是钝化层问题?怎么才能判定?在芯片边缘。

回复:

这是钝化层crack,metal没有crack。也有可能深宽比太大顶层metal太厚 passivation拉crack了。

3.问题:

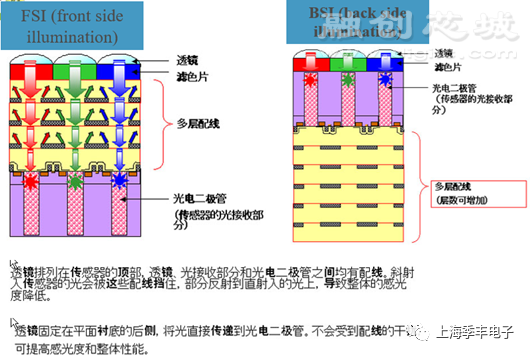

图像传感器CIS(CMOS Image Sensor)的工艺是什么?

回复:

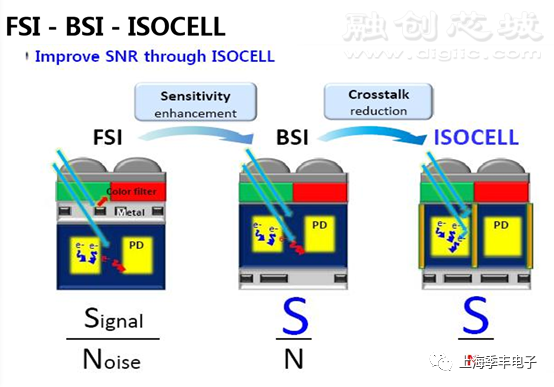

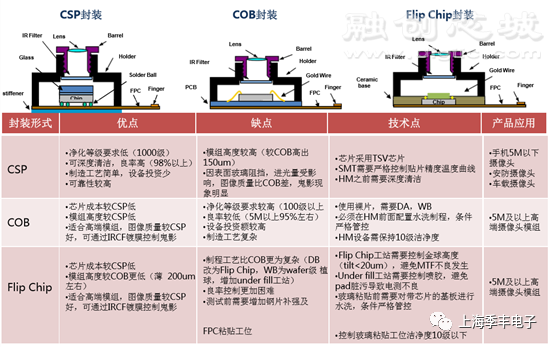

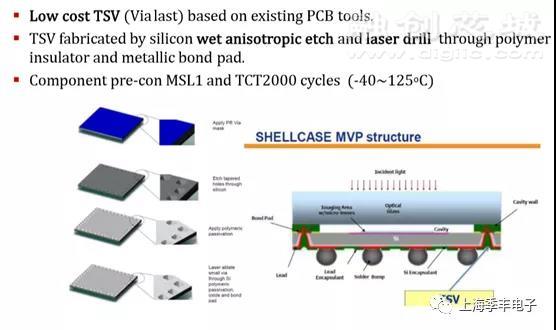

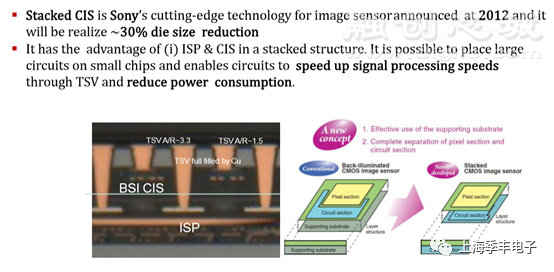

模组中Sensor,ISP,DRAM hybrid bond叠在一起。模组厂可以把CIS和ISP放在一个模组有些公司的CIS的堆叠可以把PIXEL DRAM ISP做在一个wafer里。现在CIS芯片最大尺寸6000万像素。计算CIS尺寸简单的算法是pixel size 大约是 0.7-0.8um, 60M 像素阵列按照这个尺寸可以推算,然后加上周边电路估算。还有一种更快的算法就是直接看适配的镜头,例如1/4”镜头就是感光区域对角尺寸,单位英寸。芯片尺寸现在由于都是RAW DATA 所以周边电路不多高像素大约感光区域要占到85%以上了。一般的Low Cost TSV是指Aspect Ratio 比较小的孔 <1:3 提高蚀刻速率降低成本。所以一般会做taper via 而不是 straight。

4.问题:

比方说25的铜线过流如何计算呢?

回复:

根据铜的电导率,截面积来计算阻值。直流和脉冲电流的值是差异比较大的。

5.问题:

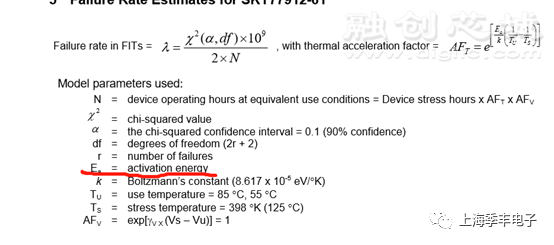

计算芯片FIT公式种Ea值怎么来的?

回复:

Ea是根据不同的失效机理, JEDEC下有一份技术参考文件: JEP122H。这个Ea值不能统一取成0.7哈,要根据各家代工厂给的值具体而定,根据fab工艺不同会有不同值。0.3~0.7之间不等。不同的Ea,整个FIT算出来差别很大,要工谨不可套用。

6.问题:

Fab做完Passivation后,通常会做1X Alloy后看有无crack,然后出货?是不是如果passivation有crack,就对同lot wafer做5X alloy进行stress看有无crack?这个alloy具体点是一种怎么样的温度和应力stress呢?

回复:

MIL标准提到的检查passivation的方法,Mil-std-883,method 2021.3。把芯片泡在酸里面,如果passivation有问题,经过酸处理,top metal会被腐蚀。OM检查即可。可以依据passivation下面的金属材质采用不同的酸。铝制程的话,磷酸,盐酸都可以。铜制程的话可以用硝酸。

也可以modify recipe. 有时可以用NaOH KOH。Alloy一般条件是270摄氏度4个小时吧这是fab制程的最后一步主要作用就是去除水汽。它的作用并不是看是否有crack。

7.问题:

fab有哪些可能的原因会导致passivation crack?

回复:

看passivation crack的严重程度,如果OM下可观察到,大概率是机械damage;如果是pin hole这种程度的微缺陷,要借助化学腐蚀放大后才能看见,高概率是arcing damage。

8.问题:

Arcing damage 电弧损伤是个怎么样的机理?

回复:

类似于PID 或者antenna effect导致GOI pinhole之类的产生机理,只不过是发生在passivation上,绝缘材料上极化电场导致的尖端放电。在 scrubber clean的过程中也有可能发生,看DI water PH值,转速等。还有一点需要注意,如果发生了wafer passivation pinhole, 芯片的CDM ESD性能很可能被影响到,需要重点check。尤其是对RF类芯片。严重的passivation pin hole通常会影响芯片性能测试,尤其是对analog和RF。TC比较适合抓passivation crack, BHAST是更合适的方法。

9.问题:

封装厂bake条件一般是125C/8小时?如果那种存有数据的flash或者eeprom之类的也是这么bake吗?

回复:

存储的一般会在wafer level做存储IP CP1测试,然后bake 150°24h再测CP2,把存储不良的rej.掉,剩下的封装,最后封装好的烘烤125度 8hrs是没有问题的,很多大厂要求出货必须烘烤的。封装厂post molding curing都是几个小时的,不影响data retention performance。data retention是一个可靠性测试项目,JESD22-A117uncycled high temperature data retention, Tj>125C 1000hours。

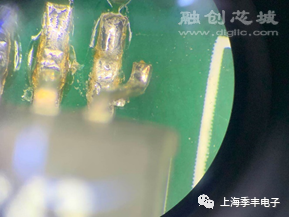

10. 问题:

下图异常图片,对于这种偶发性的焊接失效,且每次出现不良约百分之零点几,短时间或常规测试又是导通pass的情况,做震动筛选有必要吗?对于这种大PIN脚钢网开孔都是外扩保证锡量足够,看不良时PCB pad锡量是足够的而且flux也都包裹住了器件管脚(器件已经超期),如果管脚表面氧化拒焊,工艺上还需要往哪方面改进?共面性无异常。

锡膏日本的,flux含量11.5已经算最高的了,这失效不良数量不多而且可检测性差(现在好后面可能就NG,时不时的就蹦出来或者客诉,特别烦,想解决它。我们要求是无铅工艺,现在是我们功能维修在分析时定位到这个管脚,镊子拨动后发现虚焊。

分析认为是管脚氧化,导致润锡不良。

回复:

热的时候好,冷了再测问题就多,是器件封装用错料,用了有铅的。如果批量后反复复测不确定故障率,芯片封装内出问题可能性更大。

11. 问题:

QFP产品的封装一般分层有哪几种情况的分层呢,引起的原因分别是什么,都对芯片会有什么影响?

回复:

最多的是内引脚和支撑杆区域的剥离,TC/CB造成的概率最高。主要影响可靠性

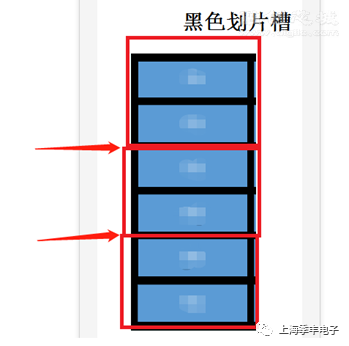

12. 问题:

跟大家咨询下:2个芯片为一组的(芯片和芯片之间包含了划片槽),在划片量产上面是否有任何影响,是否存在划偏的风险?如图:黑色为划片槽,红色为划片后的一组芯片。一组中是包含了划片道,主要是die与die的特征点是一致的,首刀落刀位置难固定,导致无法量产(工程这块是没有问题)。

回复:

切割 index 设定为一组 的 index,识别 mark 不要跟 一个 芯片的 识别mark 搞混,就可以切。软件设置的问题,如果切偏就是机台的问题。特征点一致就麻烦,如果间隔太小,在一个识别窗口内,就可能误认。还有就是disable 特征点识别,设定固定 index,这个有风险。措施:1改特征点,2. 咨询是否设置可以超出 index 偏离范围报错3. 用 dummy wafer 实际做一下关特征点识别,固定 index 盲切,monitor 一下风险。更改特征点:靠近边缘的一些die在芯片上面增加标记

13. 问题:

WLCSP焊在板子上做可靠性,UHAST和TC500之后发现有漏电,在之前一起进炉子的一批中样品中MSL1之后有发现过如图片所示的锡膏溢出。是不是可以猜想漏电问题和SMT所采用的锡膏有关系?

回复:

uHAST和TC都没达到锡膏的熔点,不影响。但是MSL有reflow,会有影响。可以改下钢网,减少锡膏量。

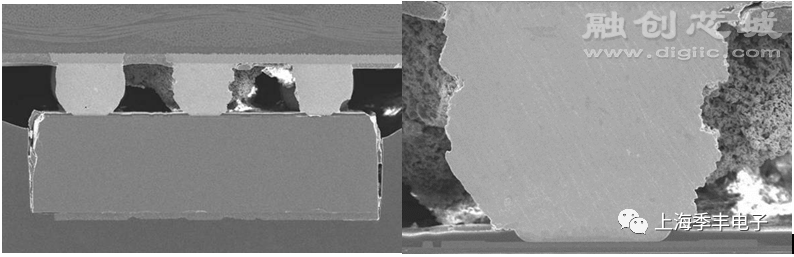

14. 问题:

WLCSP产品,板级可靠性PCT测试后short,直接在板上做的切片,结果如下。smt跟其他样品一起做的啊,uhast,tc,htsl都pass,只有pct fail。在这个之前做了另一个产品的pct,pass。这个产品做了两次试验,共三个lot,都死在pct上,其他都pass

而且两次试验不是同事做的,中间还间隔了几个月。中间间隔这段期间做了另一个产品,pct pass。

回复:

建议直接裸片做PCT看球形,不用测试数量翻倍,如果球形都是完好的,可以认为此类问题与SMT相关。这种随机性的,再现性不好的是不好说,所以做个拖底的方案,不至于走不下去。应该是100%RH的影响。如果上电有电位差,可能是金属离子迁移。有点类似HAST RDL Cu migration。还是要有持续的电势差,再加上水气,只要时间足够长都能长一起。

15. 问题:

没有烘烤的封装会影响ESD吗?里面有水汽?

回复:

这个问题可以分解讨论。1)环境湿度对ESD测试一定有影响 2)器件的ESD等级是否因为器件有无烘烤有变化。我的看法是湿度在管控范围内对于不同的湿气饱和度,抗ESD -HBM, CDM等级不变。湿敏感器件没有烘烤,主要问题在于Delam。通常器件吸湿都有饱和度,不会对ESD等级有影响。环境的高湿度可以降低ESD产生的风险,但不利仓储。所以RH在晶圆,bump,package,测试都有高低线管控。好的封装正常pitch芯片也不应该带很多湿气,感觉不ESD应该大差别。一般不会对HBM有影响,不够干燥只会影响CDM放电波形重复性不好,但结果不会变差。CDM机理就是静电在被测器件的累积效应,而体积越大静电累积越大。recon panel 12”差了很多,简直无法用unit level的数据。国内如果有作bump Fanout 的制程,这个问题一定要注意克服。CDM目前基本上都是感应式充放电,panel level CDM 几乎不测,偶尔测试还需要看大小,不好摆放,直接影响结果,另外从IV 不好判断结果,可以肯定的是结果肯定不同(体积大,等效电容也大,),采用Socket CDM 应该可以更好的对比。观察过Panel level CDM 放电波形,其宽度基本是标准波形的两倍。

16. 问题:

DDR4 DRAM工业等级规范的可靠性测试标准是什么?相比商规,在测试项目和条件上有哪些需要特别注意的,或是有没有参考的标准?

回复:

可以参考JEDEC047。

17. 问题:

失效样品返回后二极管器件特性都在,电流输出异常。怀疑输出端有断路。XRAY decap 都未发现异常。delayer之前,做什么项目好一点?

回复:

一般要做EMMI, InGaAs,OBIRCH来定位失效点,然后再做die的破坏性分析,比如研磨,FIB

18. 问题:

选择EMMI INGAAS OBIRCH具体参考什么条件更好呢?

回复:

这主要是看哪种能够清楚看到异常点即可。波长不一样。EMMI,InGaAs适合于半导体相关失效,OBIRCH适合于线性电阻特性失效,芯片后段失效问题。

19. 问题:

Decap后EFA还能做么?

回复:

Decap 后EFA可以做,因为线都连着。实在不行还可以re-bonding。

回复

回复

举报

举报

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主