|

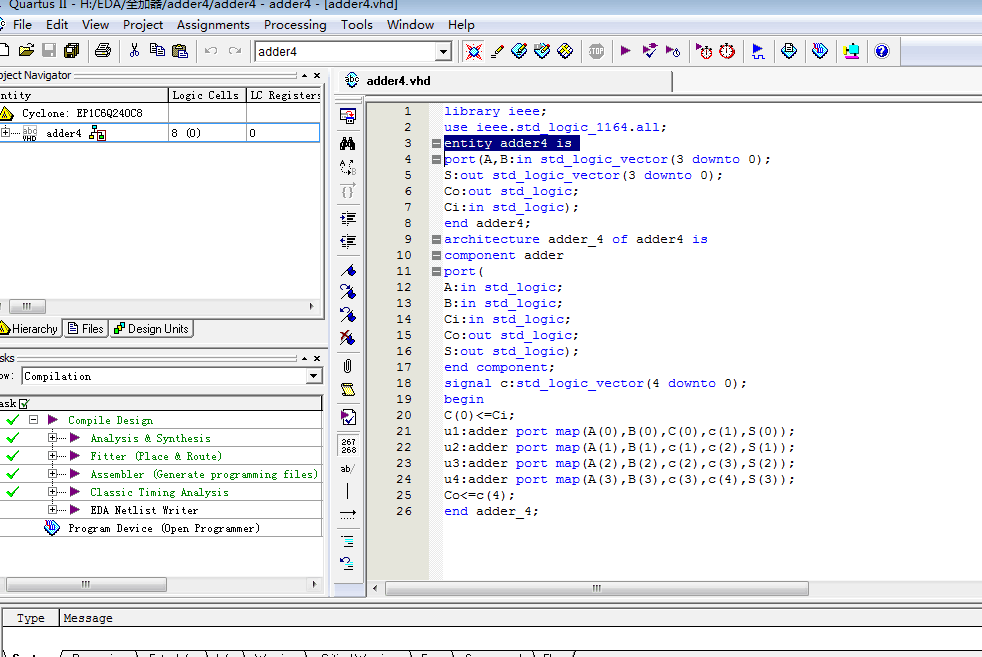

library ieee; |

回复

回复

举报

举报

-

- 0000000000000000

-

1888 发帖7917 回复34980 积分

- 私信他 +关注

回复于 2018-05-30

3#

回复于 2018-05-30

3#

-

- phoenix20111116

-

124 发帖361 回复1671 积分

- 私信他 +关注

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主