1.问题:

一般Copper Pillar Flip-chip 完后 TTV的经验值是多少?

回复:

5um以下。

2.问题:

Raw wafer中BMD (Bulk Micro Defect) 对金属离子的Gettering能力到底有多强?对于存储器及CIS等产品为啥封装厂polishing后就容易出现leakage等问题?

回复:

产品上发现的polish引起的Cu离子沾污的问题?靠BMD来Gettering是不够的,应该还要有Gettering source,类似C,F,位错聚团,远离active area。封装厂的polish应该是没有化学过程,纯粹的机械抛光,表面损伤太大,而且金属沾污的控制精度和FAB不是一个数量级的。用TXRF来看Cu ion在wafer晶背上,不同的backside polishing和 BG wheel确实有些差别。Raw wafer里面的BMD并非是为后序工艺考虑,是不是更多的是考虑是单晶本身的电阻和漏电特性,这个太高太低都不行,再加上现代的foundry process的先进性,金属离子污染的可能性也不大,很多工厂在Qual.的时候Vt stability都不做了。真正的吸杂还得要封装backside grounding来形成,即使是disco的GDP(Gettering DP (Dry Polish))技术也是这个道理。从disco GDP过的crosssection图片来看,表面还是有层缺陷层,这层既能防止薄片破裂,又能阻挡金属离子扩散进去。这一层位错可能是类似于表面渗碳+接触焊接的原理造出来的。不管是NAND还是DRAM都对铜离子敏感,尤其是比较薄的情况下。CIS的BSI polish要求的厚度比DRAM的可是要小十倍,减薄工序抛光的话也是会有问题,行业里面也是有lesson learn存在的。如果封装晶背研磨的环境差(铜离子或碱金属离子浓度高),估计GDP抛过的wafer也够呛。另外,Cu离子可能来自于固定研磨颗粒的粘合剂。

3.问题:

Pad window可以做到多小?封装厂给我们的限制是做到60um以下会影响可靠性?是这样吗?因为我们有看到少数原厂做到了50。现在业界水平应该可以做到什么程度了?产品是MCU。

回复:

看封测厂的制程能力(量产能力和设备能力),PAD window留得大,封装厂就好生产。PAD window留得小,如果制程能力强就不受影响。目前60*60就是普通水准了。大厂可以做到40x40。0.7mil Cu线,Pad做45um没问题。Pad做的小的话,最多TC担心点吧,wire pull ,ball shear, IMC 过了问题不大。Pad太小也得考虑CP的状况。CP测试主要是关心针痕,一般针痕要求不能超过25%。Pad变小,对于CP测试要求就变高。还要考虑PAD 间距,pad间距,或者pad pitch和针卡有关。PAD 做小,面积缩小了。但对封测厂的制程能力要求也提高了。经济成本不一定合算,所以要综合考量。

4.问题:

请教一下群里朋友,世面上有那种针对芯片从卷带上拿下来了,但是我要挑片子后再手动卷回tape & reel的方法或者手动机台吗?

回复:

网上就有这样设备。挑好片之后要把tape贴好,要不然容易peeling。操作的人员细心点,拆和装的时候别把覆带弄破就行了。也可以热封。

5.问题:

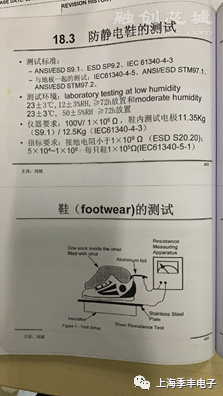

请问防静电鞋阻抗是怎么测试的?

回复:

使用TRek阻抗测试仪测试的。

6.问题:

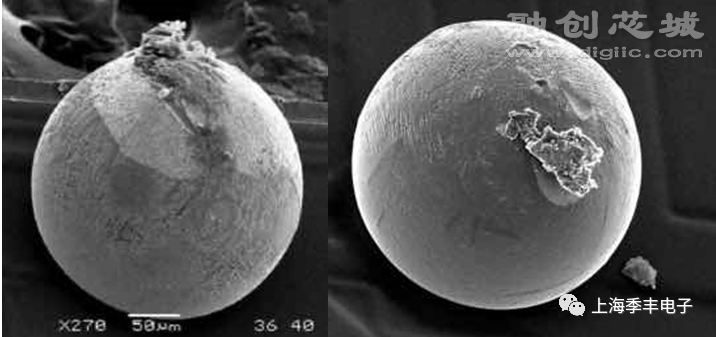

做了个实验,将锡球SAC305或者SAC405直接放在PCT条件96小时, 预处理没做,在显微镜下球表面有脱落?在双85下是没有失效。只是在PCT下失效了。不确定是否是氧化,因为锡球在PCT这个条件下开始发生反应,球表面有脱落.

回复:

考虑水汽引起的分层断裂。在双85实验下,几百小时,会产生锡球氧化开裂。

7.问题:

季丰可以测量Power MOS的SOA曲线吗?

回复:

SOA是TLP一个feature,普通TLP不带,季丰刚刚到了一台新TLP,专门带了SOA功能。

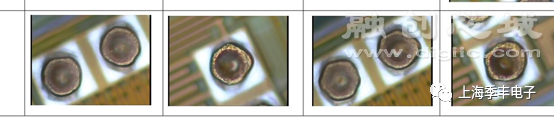

8.问题:

这种变形是什么原因?

回复:

线有受损,或者设备的送线系统有问题。

9.问题:

Bench测试的时候用力压一下芯片的表面,基准电压会变小1~2mV,竞争对手的芯片压了就基本没有变化,这种是die的原因还是封装的原因啊?封装形式一样的,板子也是同一块,焊接和socket都试过,都是一样的。QFN封装。验证的有3种芯片,1是竞争对手芯片,2是我们家A种molding compound芯片,3是我们家B种molding compound芯片,2和3都有电压变化,1基本没有变化,不是用手指压的,是用一个硬的东西压的芯片表面,基本可以排除温度影响。

回复:

碰到过,当时的芯片是Band Gap设计问题,受应力影响导致基准电压漂移,不仅测试用力加压漂移,HTOL/TCT也会导致基准电压漂移。用不同组芯片验证,相同数目样品做可靠性和相同数目不做任何试验,可以看到漂移。Bandgap设计修改后,有改善。曾在封装厂见过基准芯片432产品,TO-92/SOT89封装基准电压受应力影响偏移,作业方法是开盖再量测,通过这个方法确定是否是应力问题;最后结论是改善封装材料。这是典型的stress sensitive product, 如果不改package,你可以加gelcoating process试试。可以把你竞争对手的片子切了看看有没有gel coating,或者是怎样的封装结构。若果改封装形式,陶瓷封装和PMQFN等有cavity的封装都可以选,但陶瓷封装成本较高。

10.问题:

BGA产品在振机试验后,边角部分Ball与基材部分开裂?之后怎么排查?我们有确认过红墨水,确定边角部分断裂,有确认过IMC,确认厚度符合要求,接下来还有什么方向可以做?

回复:

振动机要排除的是产品间的碰撞。如果存在这种碰撞,那么四角的磨损从方型渐变成圆形,是一个大概率事件。以前在抖动盘发现,QFN5x5就会有这种明显现象。

11.问题:

请问打磨了QFN封装的表面丝印,是否会对封装内部或焊接产生影响?

回复:

表面打磨一般不会。看余量,磨标打标不是常规制程,一般都小工厂做的,实际是控制不好余量的。如果是打线制程的话,需要要考虑下线弧高度,小厂控制不好,也许会把线磨出来了。类似很薄的封装要忌讳这点,因为再次laser mark也会吃compound。可以先用xray看一下下面打线情况,弧高,和顶部的空间。对质量和可靠性要求较高的公司一般不会允许这种sanding & remarking的做法,除非工艺稳定且有大量数据表明这么做没问题。这种工序手工操作绝对禁止。

几个问题必须注意:

1. QFN是标准封装形式,POD的尺寸范围是固定的,没有客户的允许,绝对不能超出,否则客户完全可以认为是不良品而退货或要求赔偿,而这种打磨工序极有可能导致芯片过薄,assembly即使破例接受了,在smt那里可能也不顺利,比如吸不起或抛料等问题

2. 可能会导致mold cap过薄甚至exposewire,前面已经有朋友说过了

3. sanding过程是post assembly行为,期间如果应力较大或过分集中可能导致内部分层甚至NSOP或NSOL,极端情况下还可能有die crack.所以万不得已必须打磨的话,要对sanding process进行qualify,有问题绝对不能冒然蛮干

4. 手工打磨一般会导致方差太大,即使你有比较好的jig,机器的自动打磨工艺比较容易控制,一致性比较好,但工艺开发和设备都是成本。

如果量小,客户要求不高而且比较随意,就不用讲究了。

是wrong mark而且客户给waiver才这么干呀,否则就是不规范的市场才有的行为。一般来说,发生wrong mark,应该先和客户协商,保证traceability,让客户接受这笔料,而不是做sanding & remarking。

12.问题:

BGA芯片2个IO pin之间短路,芯片静态条件下测量2个IO之间没有短路,但是上电后,断电再测试2个IO之间就短路,这是什么原因呢?

回复:

1. 季丰3D xray可以帮助你清晰看清楚两个线直接的细微间距。如果确认没有线线间无短路,就是die里面问题了。

2. 有些芯片设计为了平均功耗,启动的缺省设置是会导致芯片较大电流的。类似这个,要问设计了。

13.问题:

行业内对IC产品的质量有等级划分吗?是参照什么标准划分的?

回复:

常用的是JEDEC标准:J-STD-020。一般就是商业等级,工业等级,车规等级,军用等级。具体还有可能细分。像MSL等级一般分1/2/3。ESD等级也有分级。

14.问题:

国军标(GJB33, GJB597等)美军标(MIL-PRF-19500等)有对电子元器件质量保证等级的划分,主要是军用等级细分。我查到网上也有商业等级,工业等级,车规等级,军用等级说法,但是没有查到对应的参考标准,不知道您是否了解相关标准(比如商用级划分标准,工业级划分标准等)?一般IC器件上会标识质量保证等级吗?

回复:

一般是温度划分的。商业级器件的工作温度范围是0℃~+70℃,工业级的是-40℃~+85℃,军品级的是-55℃~+150℃。另外还有些器件有一种汽车工业级的是-40℃~+125℃。这都是一些常规粗分。具体看产品的。主要影响在于温度 design margin, 特性分析和量产的温度控制范围。

AEC-Q100里,汽车电子标准,automotivegrade:

Grade 0 -40°C +150°C

Grade 1 -40°C +125°C

Grade 2 -40°C +105°C

Grade 3 -40°C +85°C

15.问题:

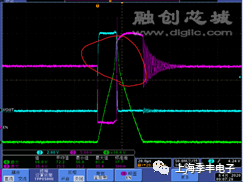

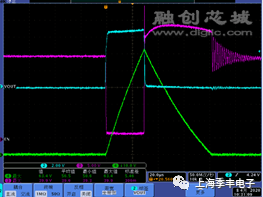

测试MOS的UIS时,68A电流用小电感5uh,会出现充电电流匀速上升后忽然速度加快。如下图。

电感加倍10uh后,充放电就正常。这是因为什么原因呢?小电感饱和了?Channel2 是Gate电压。Channel3 是Drain电压。Channel4 是Drain上电流

5uh的是小电感

10uh是大电感

回复:

电感可以在负载电流下测试感量,你看看感量对不对。电感单体感量测试用的是LCR表,如果需要测试最大电流,需要配置专门的负载电源,这个一般电感厂才有。

16.问题:

常规可靠性试验中 PCT 和 UHAST 可以等效吗?PCT不是偏应力试验吗,为什么可以等效?是否有原理或者标准做依托?

回复:

PCT和uHAST都能考量封装气密性,不同的是PCT的失效机制是化学金属腐蚀,uHAST的失效机制是电离腐蚀。

回复

回复

举报

举报

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主