分享到:

XRAM是一种新的存储器体系结构,旨在以具有竞争力的价格提供高密度和高性能RAM。XRAM使用先进的DRAM技术和自刷新体系结构,显着提高了存储器密度,性能并简化了用户界面。

XM8A51216是星忆存储科技公司生产的一颗16位宽512K(512*16,即1M字节)容量的CMOS静态内存芯片。该国产SRAM芯片具有如下几个特点:

⚫高速。具有最高访问速度10/12ns。

⚫低功耗。

⚫TTL电平兼容。

⚫全静态操作。不需要刷新和时钟电路。

⚫三态输出。

⚫字节控制功能。支持高/低字节控制。

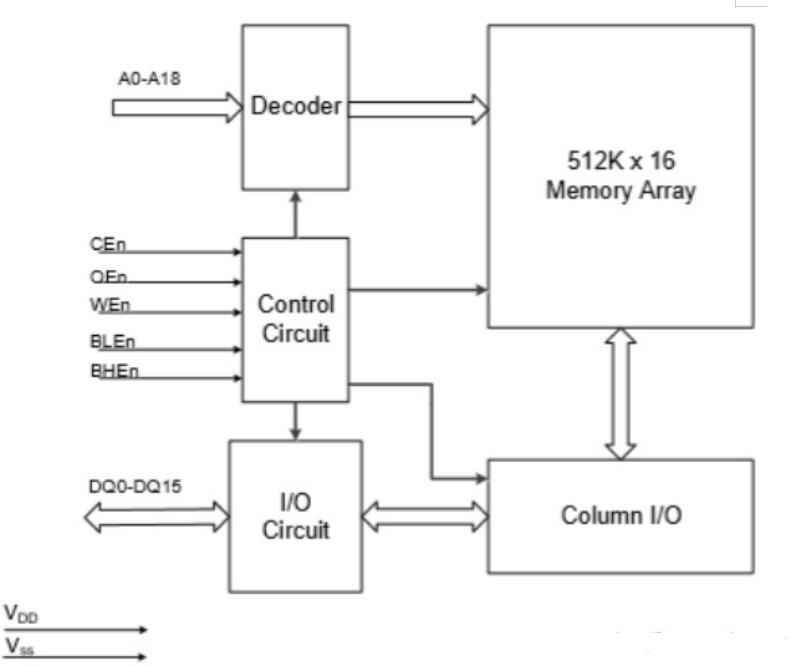

XM8A51216功能框图

图中A0~18为地址线,总共19根地址线(即2^19=512K,1K=1024);DQ0~15为数据线,总共16根数据线。CEn是芯片使能信号,低电平有效;OEn是输出使能信号,低电平有效;WEn是写使能信号,低电平有效;BLEn和BHEn分别是高字节控制和低字节控制信号;

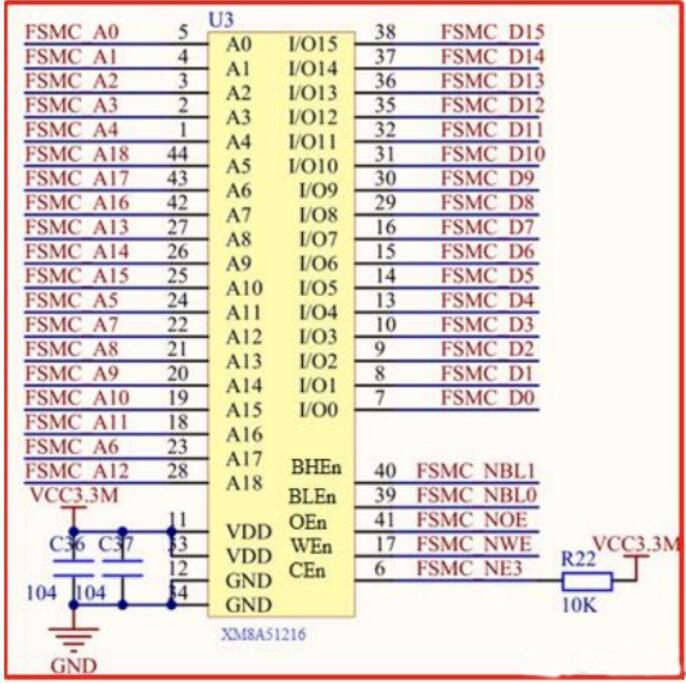

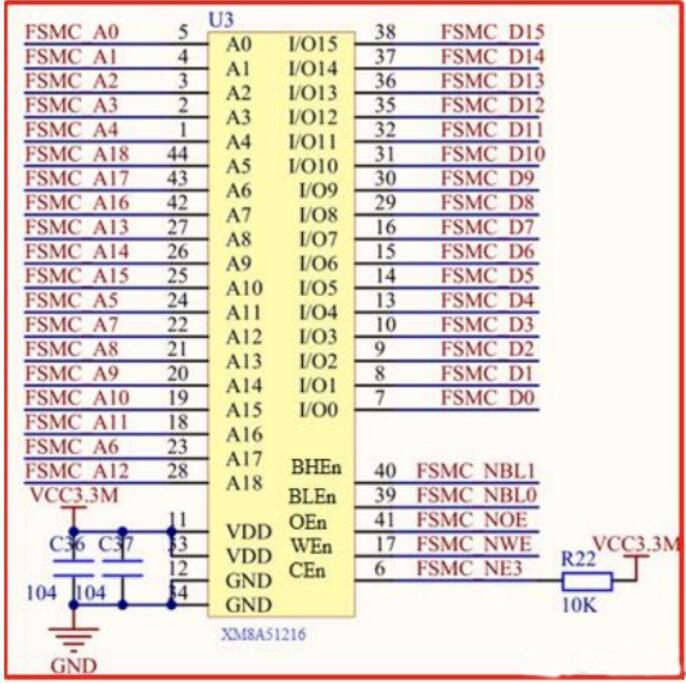

XM8A51216原理图

XM8A51216在功能上等效于异步SRAM,是一种高性能8Mbit CMOS存储器,组织为512K字乘16位和1024K字乘8位,支持异步SRAM存储器接口。代理商英尚微电子支持产品相关技术支持及解决方案。

要写入设备,请将芯片使能(CE)和写使能(WE)输入设为低电平。如果字节低使能(BLE)为低,则来自I/O引脚(DQ0至DQ7)的数据被写入地址引脚(A0至A18)上指定的位置。如果字节高使能(BHE)为低电平,则来自I/O引脚(DQ8至DQ15)的数据将写入地址引脚(A0至A18)上指定的位置。要从器件读取,请将芯片使能(CE)和输出使能(OE)设为低电平,同时将写入使能(WE)设为高电平。如果字节低使能(BLE)为低,则地址引脚指定的存储器位置中的数据出现在DQ0至DQ7上。如果字节高使能(BHE)为低,则来自存储器的数据出现在DQ8到DQ15上。

取消选择器件(CE),禁用输出(OEHIGH),禁用BHE和BLE(BHE,BLEHIGH)或以下操作时,输入或输出引脚(DQ0至DQ15)处于高阻抗状态写操作(CE和WELOW)。突发模式引脚(MODE)定义突发序列的顺序。当置为高电平时,选择交错的突发序列。当拉低时,选择线性突发序列。

XM8A51216是星忆存储科技公司生产的一颗16位宽512K(512*16,即1M字节)容量的CMOS静态内存芯片。该国产SRAM芯片具有如下几个特点:

⚫高速。具有最高访问速度10/12ns。

⚫低功耗。

⚫TTL电平兼容。

⚫全静态操作。不需要刷新和时钟电路。

⚫三态输出。

⚫字节控制功能。支持高/低字节控制。

XM8A51216功能框图

图中A0~18为地址线,总共19根地址线(即2^19=512K,1K=1024);DQ0~15为数据线,总共16根数据线。CEn是芯片使能信号,低电平有效;OEn是输出使能信号,低电平有效;WEn是写使能信号,低电平有效;BLEn和BHEn分别是高字节控制和低字节控制信号;

XM8A51216原理图

XM8A51216在功能上等效于异步SRAM,是一种高性能8Mbit CMOS存储器,组织为512K字乘16位和1024K字乘8位,支持异步SRAM存储器接口。代理商英尚微电子支持产品相关技术支持及解决方案。

要写入设备,请将芯片使能(CE)和写使能(WE)输入设为低电平。如果字节低使能(BLE)为低,则来自I/O引脚(DQ0至DQ7)的数据被写入地址引脚(A0至A18)上指定的位置。如果字节高使能(BHE)为低电平,则来自I/O引脚(DQ8至DQ15)的数据将写入地址引脚(A0至A18)上指定的位置。要从器件读取,请将芯片使能(CE)和输出使能(OE)设为低电平,同时将写入使能(WE)设为高电平。如果字节低使能(BLE)为低,则地址引脚指定的存储器位置中的数据出现在DQ0至DQ7上。如果字节高使能(BHE)为低,则来自存储器的数据出现在DQ8到DQ15上。

取消选择器件(CE),禁用输出(OEHIGH),禁用BHE和BLE(BHE,BLEHIGH)或以下操作时,输入或输出引脚(DQ0至DQ15)处于高阻抗状态写操作(CE和WELOW)。突发模式引脚(MODE)定义突发序列的顺序。当置为高电平时,选择交错的突发序列。当拉低时,选择线性突发序列。

(0 )

(0 )

回复

回复

举报

举报

发表回复

版

块

导

航

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主