18.SRIO接口

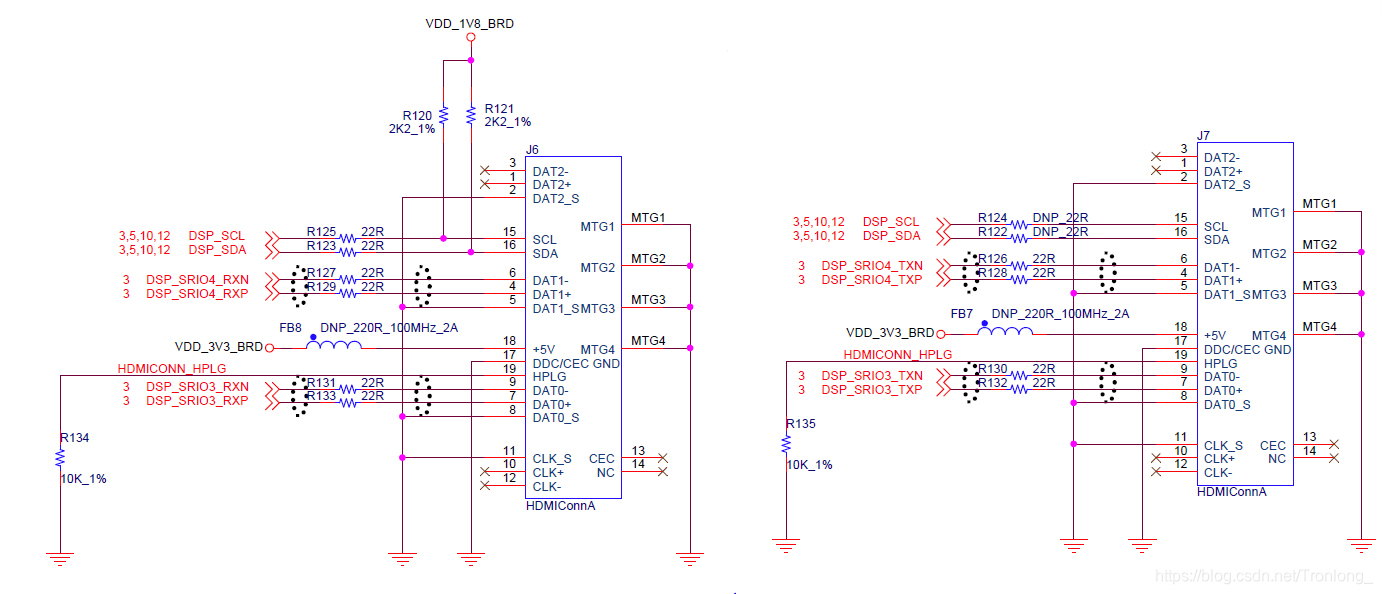

SRIO由SRIO RX(J6)和SRIO TX(J7)组成(DSP端),以2个HDMI接口形式引出,支持4路数据传输,最高传输速率为5GBaud,硬件及引脚定义如下图:

图 53

图 54

19.PCIe接口

开发板引出了PCIe Gen2接口(J4),2通道,编码方案为8b/10b,总共64pin,主接口区42pin,单通道理论最高传输速率达5GBaud,总传输速率为5GBaud*8/10=8Gbit/s,硬件及引脚定义如下图:

图 55

图 56

20.模式调试接口

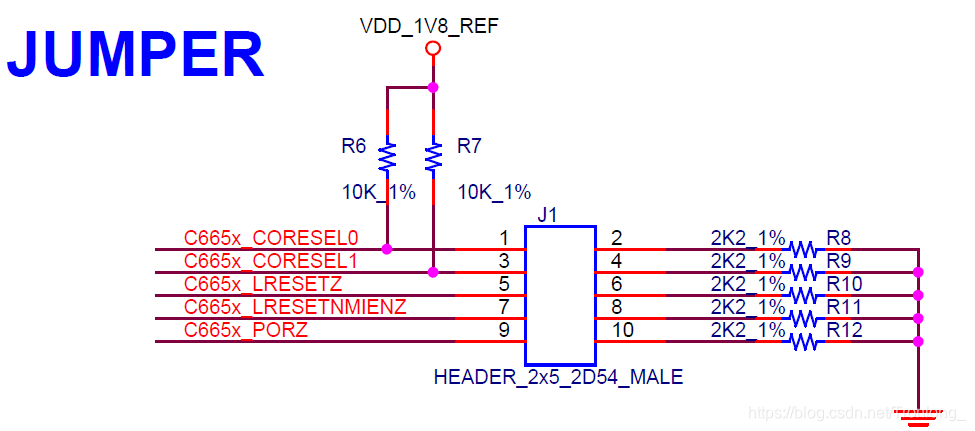

开发板J1为模式调试接口,采用2*5pin、2.54mm间距双排针连接方式,主要用于复位、NMI等调试,硬件及引脚定义如下图:

图 57

图 58

CORESEL0/CORESEL1:核心选择管脚,用于选择启动或者复位的核心。

LRESETZ:Warm Retset软复位管脚。

LRESETNMIENZ:模式选择使能管脚。

PORZ:上电复位管脚,用于上电时的复位行为。

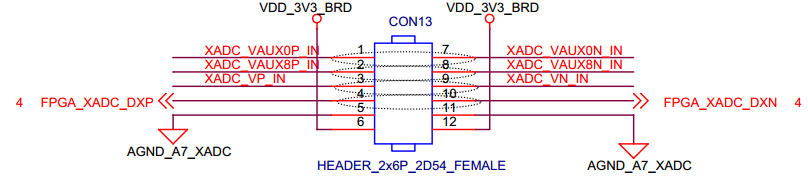

21.XADC接口

开发板引出了FPGA内部XADC信号(CON13),硬件及引脚定义如下图:

图 59

图 60

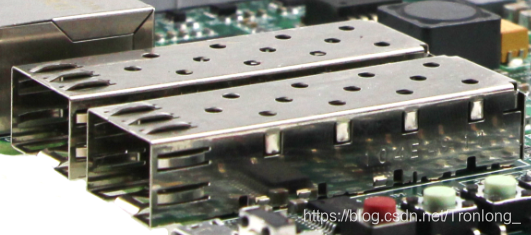

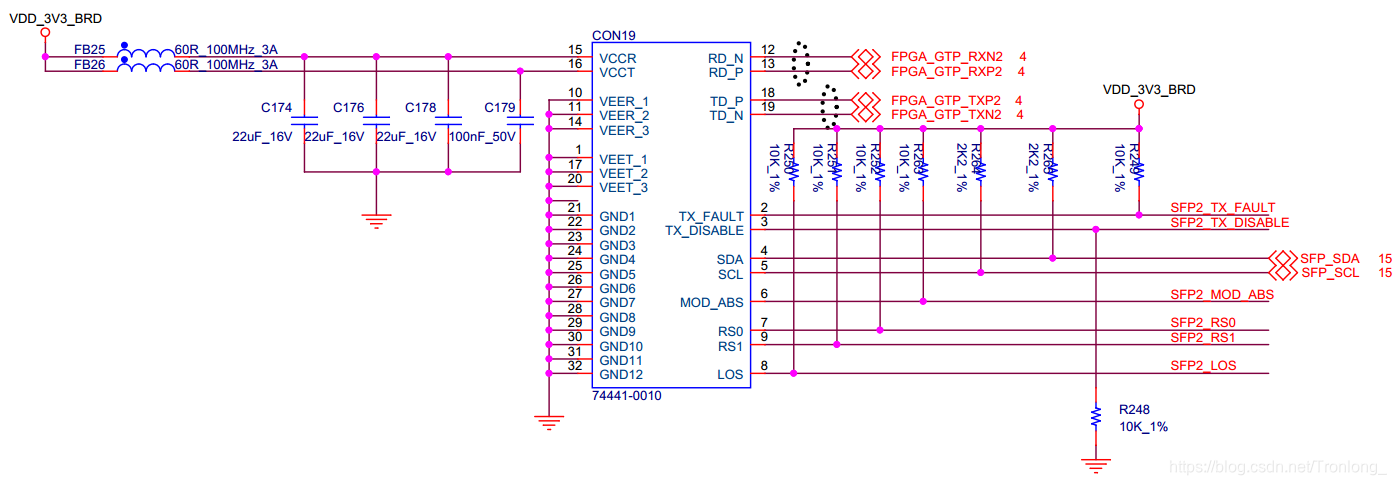

22.SFP光纤接口

SFP光纤接口由SFP1(CON14)和SFP2(CON19)组成(FPGA端),传输速率可高达5Gbit/s,硬件及引脚定义如下图:

图 61

图 62 SFP1

图 63 SFP2

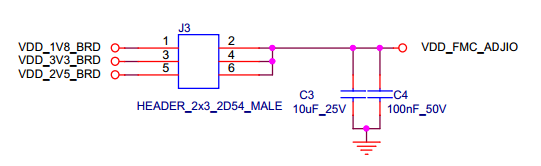

23.BANK电压

开发板引出一个BANK电压(J3,FPGA端),1.8V、2.5V以及3.3V可选,硬件及引脚定义如下图:

图 64

图 65

回复

回复

举报

举报

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主