高速数据采集系统目前已在雷达、声纳、软件无线电、瞬态信号测试等领域得到广泛应用。它的关键技术是高速 ADC 技术、数据存储与传输技术和抗干扰技术。本文在分析了高速多通道数据采集系统中存储子系统的性能要求和设计方案的基础上,提出了高速缓存和海量缓存方案,并将该方案成功地应用于 DSP 多通道超声信号采集与处理系统中。

对高速多通道采样数据存储的性能要求:一是高速性,现在高速数据采集中所用的 ADC 已达到几十甚至几百 MSPS 的水平,这就要求采样数据存储器的速度也要与之匹配,也就是采用高速缓存;二是大容量,其原因是多通道高速数据采集会产生巨大的数据流。一个4通道40MHz采样率16位精度数据采集板并行采样0.1s将产生32MB的数据量,所以,通常需要海量缓存来存储采样数据。

2、高速缓存的实现

通常构成高速缓存的方案有三种:

第一种是 FIFO(先进先出)方式。FIFO 存储器就象数据管道一样,数据从管道的一头流入、从另一头流出,先进入的数据先流出。FIFO 具有两套数据线而无地址线,可在其一端写操作而在另一端读操作,数据在其中顺序移动,因而能够达到很高的传输速度和效率,且由于省去了地址线而有利于 PCB 板布线。缺点是只能顺序读写数据,因而显得比较呆板,而且大容量的高速 FIFO 非常昂贵;

第二种是双口 RAM 方式。双口 RAM 具有两套独立的数据、地址和控制总线,因而可从两个端口同时读写而互不干扰,并可将采样数据从一个端口写入而由 DSP 从另一个端口读出。双口 RAM 也能达到很高的传输速度,并且具有随机存取的优点,缺点是大容量的高速双口 RAM 很难得且价格昂贵;

第三种是高速SRAM 切换方式。高速SRAM 只有一套数据、地址和控制总线,可通过三态缓冲门分别接到 A/D 转换器和 DSP 上。当 A/D 采样时,SRAM 由三态门切换到 A/D 转换器一侧,以使采样数据写入其中。当 A/D 采样结束后,SRAM 再由三态门切换到 DSP 一侧以便 DSP 进行读写。这种方式的优点是SRAM 可随机存取,同时较大容量的高速SRAM 容易得到且价格适中,缺点是切换控制电路比较复杂,且只能由 A/D 转换器和 DSP 分时读写。

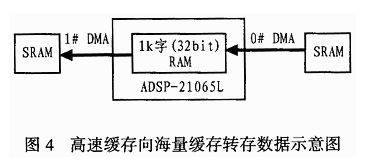

综合考虑以上三种高速缓存方案的性能、价格和实现方便性后,笔者选用第三种方案(即高速SRAM 切换方式)来构成 A/D 采样高速缓存。系统的采样与存储部分的原理框图如图1所示。

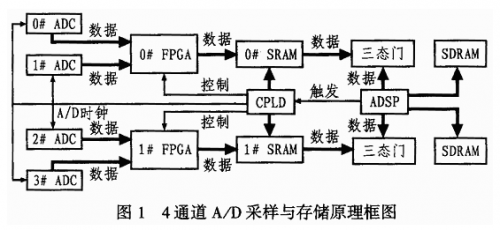

图1中,SRAM 选用IS61LV25616-10T,容量为256k16bit,访问速度为10ns,使用两片即可构成256k32bit的高速缓存。当一轮采样开始时,DSP 发出触发信号给CPLD,后者对50MHz晶振时钟二分频后得到25MHz采样时钟提供给4路 A/D 转换器AD9225,同时对4路超声信号进行25MHz、12bit的 A/D 转换。转换结果分成两个完全一样的数据通道进行处理,每个数据通道处理两路 A/D 转换结果,每个数据通道包含一片 FPGA(现场可编程门阵列)、一片SRAM 及其后的数据三态门等电路。FPGA 可接收两路 A/D 转换结果并在其内部进行复用,以将其变成一路50MHz、12bit的数据流送入IS61LV25616缓存。FPGA 完成数据通道复用的原理如图2所示。

FPGA 选用EP1K50,它的逻辑门数为5万门,内含10个EAB(嵌入阵列块)。每个EAB实际上是4kbit的 RAM,可以用来构造 FIFO、双口 RAM 等。本系统应用两块EAB构成了两个25616bit的 FIFO,因而可将两路 A/D 转换结果分别送入两个 FIFO,然后在 FPGA 的输出端将两个 FIFO 中的数据交替地读出写入IS61LV25616,每个 FIFO 每次读出128个采样数据。A/D 转换器的输出为12位数据,而 FPGA 的片内 FIFO 和片外IS61LV25616的数据字宽都为16位。在存储、传送时,将高4位补0即可。两路 A/D 采样速度都为25MHz,复用后输出的速率为50MHz,这个速度对于IS61LV25616和EP1K50都是完全可以达到的。FPGA 的作用除了构造 FIFO 以实现数据通道复用外,还可以作为协处理器由板上 DSP 控制来进行一些简单高效的数据预处理(如插值、取平均、FIR滤波等)。同时可使用EDA工具MAX+PLUSⅡ10.0来对EP1K50的逻辑算法进行设计、编译并仿真,然后下载到EP1K50中实现预定功能。

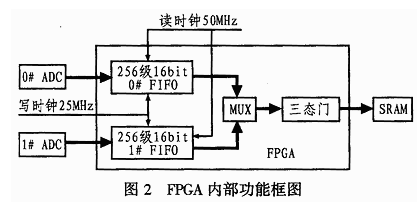

除了 FPGA 外,系统还采用了一片CPLD(复杂可编程逻辑器件)来控制采样。前者主要用于数据通道对 A/D 采样结果进行缓冲复用以及预处理,后者则负责产生 A/D 采样时钟以及作为地址计数器产生地址并提供给两片IS61LV25616以便存入 A/D 采样结果等。CPLD不象 FPGA 那样能完成较复杂的逻辑功能和信号处理算法,但是它具有更高的速度,且管脚到管脚具有固定一致的时延,因而在设计调试时容易获得简单可靠的定时关系,适于实现高速计数器、触发器、译码器等定时要求比较严格的场合。本系统使用MAX7128AE来控制采样,其可实现的功能如图3所示。

MAX7128AE可用于实现两个18位地址计数器,它具有地址总线开关切换功能,在 A/D 采样期间能以25 MHz的频率进行地址计数以作为高速缓存的地址线。当一轮 A/D 采样结束后,系统可将高速缓存的地址总线切换到 DSP 的地址总线,然后由 DSP 读取高速缓存中的 A/D 转换结果并进行处理。高速缓存IS61LV25616的数据总线一方面连到 FPGA 以便在采样期间接受复用的 A/D 转换结果;一方面则通过三态门连到 DSP 的数据总线以便在采样结束后由 DSP 读取采样数据。

发帖

发帖

回复

回复

楼主

楼主

回复

回复

举报

举报