分享到:

目前针对不同的应用市场,SRAM产品的技术发展已经呈现出了两大趋势:一是向高性能通信网络所需的高速器件发展,由于读写速度快,SRAM存储器被用作计算机中的高速缓存,提高它的读写速度对于充分发挥微处理器的优势,改善处理器性能有着积极的意义。另一个是降低功耗,以适应蓬勃发展的便携式应用市场。英尚微电子介绍关于SRAM读写中“写操作”分析。

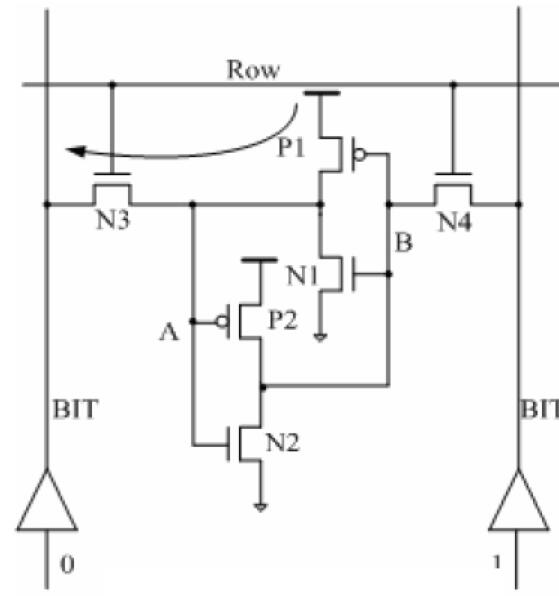

写操作与读操作正好相反,它要使存储单元的状态按照写入的数据进行相应的翻转。如图1 表示了六管单元的写操作示意图。位线BIT_在写操作开始时被驱动到低电平。在字线打开传输管后,N3 与P1 管在BIT 与高电平VDD 之间形成分压。为了写操作的成功,也就是下拉节点A 至足够的低电平,启动反相器P2/N2放大新数据,传输管N3 应该比P1 管有更好的导通性。一旦反相器P2/N2 开始放大节点A 上的低电压,也就是节点A 上的下拉管N2 被关闭,上拉管P2 被打开,节点B 的电压将上升,反相器P1/N1 也将被启动,节点A 在正反馈作用下进一步向GND 转化,写操作被加速。

图1 六管单元的写操作

在六管单元的写操作中,外部电路驱动两个互补的信号到位线BIT 和BIT_上,字线驱动器驱动字线ROW 到高电平,位线信号经两个传输管写入存储节点。如图1 所示的正是向存有“1”的单元写“0”的情况,也就是把A 点的电平由VDD 下拉至GND。

(0 )

(0 )

回复

回复

举报

举报

发表回复

版

块

导

航

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主