-

- 0000000000000000

-

1888 发帖7917 回复34980 积分

- 私信他 + 关注

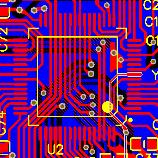

STM32H750(原理图PCB图资料分享) (M7内核,主频400M 16位AD 官网报价3美元,折合人民币20左右)

(数据手册见附件)

价格不到20人民币

1、串口最快可达12.5M,带低功耗串口;

2、128K FLASH/1M SRAM;

3、SPI最快可达100M;

4、2路12位DA、3路3.6M的16位AD;

5、22路 16位定时器和32位定时器,最高可达400M;

6、支持32位并行总线;

7、……

The STM32H750 Value line offers the performance of the Arm® Cortex®-M7 core (with double-precision floating point unit) running up to 400 MHz at an affordable price point by trimming embedded Flash to the essential. The STM32H750 Value line offer the lowest price point ever for the STM32H7 Series.

Performance

At 400 MHz fCPU, the STM32H750 Value line delivers 2020 CoreMark /856 DMIPS performance executing from Flash memory, with 0-wait states thanks to its L1 cache. The DSP instruction set and the double-precision FPU enlarge the range of addressable applications. External memory can be used with no performance penalty thanks to the L1 cache (16 Kbytes + 16 Kbytes of I-cache and D-cache).

Security

The STM32H750 integrates a crypto/hash processor providing hardware acceleration for AES-128, -192 and -256 encryption, with support for GCM and CCM, Triple DES, and hash (MD5, SHA-1 and SHA-2) algorithms. It also. It also includes security services to authenticate and protect your software IPs while performing initial programming or firmware upgrades in the field.

Power efficiency

The multi-power domain architecture allows the different power domains to be set in low-power mode to optimize the power efficiency. In addition to the main regulator featuring voltage scaling to supply the core in different voltage ranges during Run and Stop modes, the device also embeds a USB regulator to supply the embedded physical layer (PHY) and a backup regulator.

The maximum junction temperature supported is up to 125 °C, allowing to leverage the full core and peripheral performance even when the ambient temperature increases.

- 263 µ/MHz typical @VDD = 3.3 V and 25 °C in Run mode (peripherals off)

- 4 µA in Standby mode (low-power mode)

Graphics

The new LCD-TFT controller interface with dual-layer support takes advantage of the Chrom‑ART Accelerator™. This graphics accelerator creates content twice as fast as the core alone. As well as efficient 2-D raw data copy, additional functions are supported by the Chrom-ART Accelerator such as image format conversion or image blending (image mixing with some transparency). As a result, the Chrom-ART Accelerator boosts graphics content creation and saves the processing bandwidth of the MCU core for the rest of the application. In addition, the STM32H50 Value line embeds a JPEG hardware accelerator for fast JPEG encoding and decoding, off-loading the CPU which remains available for other tasks.

Integration

- Audio: Two dedicated audio PLLs, three full-duplex I²S interfaces, a new serial audio interface (SAI) supporting time-division multiplex (TDM) mode and a DFSDM (digital filters for sigma-delta modulators or MEMS microphone).

- Up to 35 communication interfaces including four USARTs in addition to four UARTs running at up to 12.5 Mbit/s, one low-power UART, six SPIs running at up to 100 Mbit/s, four I²C interfaces running at up to 1 MHz with a new optional digital filter capability, two FD-CAN, two SDIO, USB 2.0 full-speed device/host/OTG controller with an on-chip PHY and a USB 2.0 high-speed/full-speed device/host/OTG controller, on-chip full-speed PHY and ULPI, Ethernet MAC, SPDIF-IN, HDMI-CEC, camera interface, single wire protocol interface and MDIO slave.

- Analog: Two 12-bit DACs, three fast ADCs reaching 16-bit maximum resolution (3.6 Msamples/s), 22 16- and 32-bit timers running at up to 400 MHz on the 16-bit high-resolution timer. Easily extendable memory range using the flexible memory controller with a 32-bit parallel interface, and supporting Compact Flash, SRAM, PSRAM, NOR, NAND and SDRAM memories or using the Dual-mode Quad-SPI to allow code execution from an external serial Flash memory. An analog true random number generator.

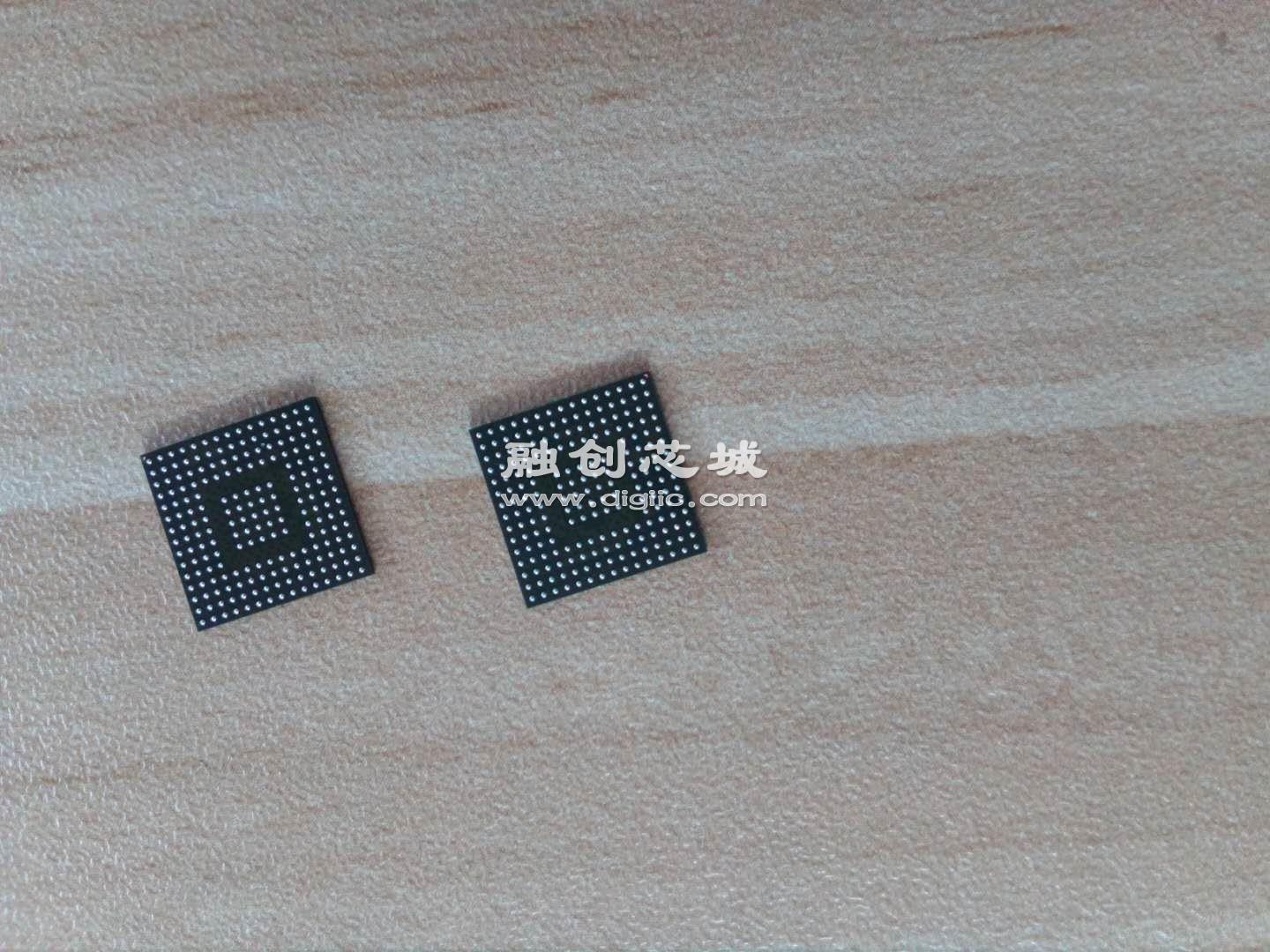

The STM32H750 Value line provides 128 Kbytes of Flash memory, 1 Mbyte of SRAM with a scattered architecture: 192 Kbytes of TCM RAM (including 64 Kbytes of ITCM RAM and 128 Kbytes of DTCM RAM for time-critical routines and data), 512 Kbytes, 288 Kbytes and 64 Kbytes of user SRAM, and 4 Kbytes of SRAM in backup domain to keep data in the lowest power modes and LQFP100, UFBGA176 and TFBGA240-pin packages in BGA and LQFP profiles.

回复

回复

举报

举报

-

- 0000000000000000

-

1888 发帖7917 回复34980 积分

- 私信他 +关注

-

- xiaomiking

-

1147 发帖6357 回复18609 积分

- 私信他 +关注

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主