1.问题:

HTOL测试之后,流过电流最大(600mA)的ball有damage,其余ball都完好,只有固定的这个ball有压伤甚至变形掉落。3个批次,每个批次都有10颗左右发生。HTOL1000已经做完了,FT结果都是pass,但确实看到这个固定的球有变形,所以怀疑是大电流过热导致。1000hrs后发现球变形,之前都ok。这颗产品上总共有3个ball 有大电流流经,另外2个ball板子上有接电容,这颗ball没有接。不同成分的锡球对电流承受能力有差别吗,我们现在用的是SAC1205,0.25的ball.

回复:

如果电流问题应该同一地方,是吗?痕迹比较好找。可能跟测试板相关 可以去检验下。好的,有没有可能是HTOL电路板设计的不够好,这个ball引出来没有接电容。相同电流的另外2个ball有电容,就是好的。是否可以外挂一个电容,再试试。可能是pcb layout或者内部设计不均衡,这个球电流更集中。以前案例:由于PCB设计以及所用材质问题导致的HTOL失效。PCB设计问题主要是过孔的设计,有没有避开ball。材质的问题就板材的热膨胀系数过大导致的形变。

2.问题:

QFN32封装,一个pin最多能打几根线?

回复:

和pin的长宽设计有关,空间够的话5根都可以打的。具体要请封装厂评估,除了要看空间大小,还要考虑molding 溢料风险

3.问题:

Pre-condition做完后到HAST, 有没有Q-time管控? 一般是卡多长时间?有一批hold超过了半个月, 需要重新做PC吗?这期间倒是都在真空袋里保存的。之前做过PC了, 只不过炉子机时一直没空, 等了半个月。

回复:

可以烘烤个4小时左右再做HAST。JEDEC标准没有明确说多长时间,一般都是4天以内。所有试验期间的样品,最好能抽真空保存。对于HAST后的Q-time,JEDEC的要求是48hrs,如果用MBB包装后可以到144hr。TH,THB,PCT有相同要求。其他的是96hr,MBB包装后到288hr。这个是样品出炉到FT结束的时间要求,也是中间读点回炉的要求

4.问题:

HAST之后需要扫SAT吗?

回复:

不需要。一般来讲precon/MSL前后需要做SAT检查,TC/HAST/HTS等测试之后只要外观和FT或OS检测,除非客户有特别要求。从可靠性测试的严谨性考虑,TC和HAST之后,还是要看一下SAT。如果是MCM package, 建议在 env. reliability stress后SAT和CA。Q104可以参考。MSL中预处理后要看IR前后的SAT结果,确认分层情况以及变化量;FA是需要看是否拆片导致的分层,可靠性试验后做的SAT,也应考虑分层变化量,建议按照MSL来判定

5. 问题:

这种焊点是枕头效应吗?

回复:

像枕头,可以用3D-Xray看。如果不良比例高,可以抽不良板做切片(破坏性),如果成品板比较小,可以考虑做3d-xray(非破坏),如果PCBA大,3D-Xray需要制样,就是破坏性了,目的都是看横截面的结合状况。可以做红墨水破坏性测试。这xray图像与探头是否在芯片正上方有很大关系。这图不能代表焊接实质。这是因为探头如果从侧面照过去,就是这种有角度的,当正上方未必。建议可以实地看看或者用3D。可以调高点电压和功率,让球亮点,再给点角度,看一下球上有没有焊盘印迹,如果有,而且印迹与焊盘边缘重合,说明是焊偏了,如果没有,说明虚焊了,可以参考下。这个印迹是球焊接好后过回流焊时留下的。但这个照片看,感觉已经给角度了,设备是否要做一下Calibration。

6.问题:

请问不用ate 实现批量的flash 和 otp烧写 (通过uart接口下载程序) 有没有现成的设备

回复:

EVBboard带socket可以实现用PC的UART口烧写,可以开发UART的脚本,自动完成。不过ATE也可以烧写,只要有pattern。一般pattern可以用JTAG口,只要DV能跑通,产生pattern给ATE。另外也可以采用下载firmware的方式,再利用UART烧写,但测试时间可能比较长。JTAG pattern方式为首选,会节约下载firmware的时间和解决UART速率低的问题

7. 问题:

对于QFN的BHAST测试考核的内容是什么?是主要考核封装还是电路?对封装和电路 考察的点是什么?bonding线的结合力?AP层开窗有水气进去?另外 有没有见过BHAST后ATE测试RF指标有退化的?

回复:

HAST试验是模拟芯片在潮湿、高温的待机状态下是否会出现失效。试验时待测芯片会被置于高温、高湿以及高压力下,湿气会沿着塑封料和金属框架之间渗入,芯片内的一些杂质会溶解在水中,在电压和潮湿环境的双重作用下,发生电化学反应腐蚀和化学反应腐蚀,从而造成芯片腐蚀失效。HAST考察的是封装,由于芯片内部上电,电路上有腐蚀导致阻抗变化,RF指标退化是正常的。

8. 问题:

裸芯片侧面有裂纹,验证它的可靠性用那些项目会比较好,目前用温度循环(-65—150度条件)。

回复:

有裂纹的话建议全套都做下吧,风险太高,PC+TC, PC+HAST或uHAST吧

以前分析过封装芯片侧裂的情况(开盖看到侧裂),产品采用5*TCT+IR*3 同时卡严相应测试项目的规格(可了解下侧裂影响的电路,然后看测试项目与之对应性,找到对应参数),100%筛选是不可能的,但可根据结果做出个有利判断,供参考.

9. 问题:

如果想看BHAST后是否由于腐蚀引起电阻变化该变化一般是在bong线上还是die内部 有什么仪器能看到这个现象吗?那如果考核下来认为fail,是要重新考虑封装BOM吗 如何应对不让湿气渗透进去?

回复:

严重的可以Decap。Fail的话要重新考虑BOM。

10. 问题:

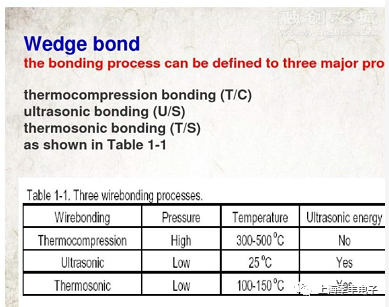

Wire bonding method:T/C or U/C or T/S 是啥缩写?

回复:

11.问题:

芯片做HTOL,要求试验前后在室温、高温、低温条件下进行参数测量,一般高温、低温应该设定在什么值,还是要根据温度等级来设定,我们产品温度等级是-40-105℃。

回复:

HTOL后通常是恢复到室温下进行参数测试,如果要三温测试,应该在产品允许的温度范围内测试,即你们产品的温度范围+常温。产品温度等级是-40-105℃,所以正常高低温也是

特性分析要再衍生5-10℃。电特性测试温度20—28℃,htol有标准多用125℃,低温军-55℃,民-40℃。不同产品都有对应标准。建议查询jedec标准,gjb标准,车规标准。一般来讲是跟着量产FT的条件走,前后都用同一条件判断,报告是报告,pass不代表无问题,内部可根据测试结果做分析,甚至再做一次char。

12.问题:

烘箱能保证精度正负1度吗?

回复:

普通的达不到,体积大的也有温度不均匀因素。烘箱把出风口塞起来,打开风扇,闷一段时间后,箱内温度是比较均匀的,可控制在1摄氏度以内(计量单位校准就是这样做的)上中下放几个温度采集探头,可以测量的。

回复

回复

举报

举报

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主