通过一个 3200Mbps LPDDR4 接口将一个应用处理器连接至 DRAM 芯片,其难度不亚于 2600MHz 4G LTE 天线的布线工作。虽然 RF 前端采用了陶瓷封装,并在各个抗电磁干扰模块中进行了精心布线,但数字信号会穿过球栅阵列封装和高密度小型印刷电路板(PCB),从而使它们更容易受到高频影响。

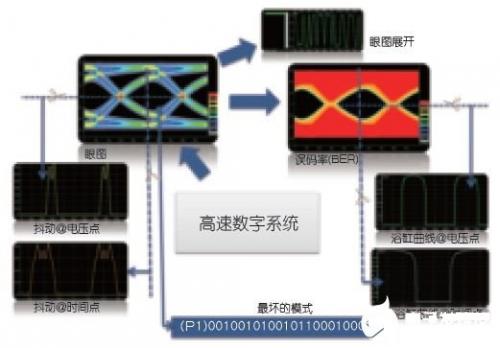

随着数据速率增至甚至超出千兆范围,PCB 印制线不能再被视为简单的导体。铜印制线的寄生电阻、电容和电感使其成为一条传输线,从而产生数字设计中通常不去考虑的各类高频效应。例如,由于集肤效应,信号的高频成分要比低频成分经历更大的衰减,从而导致信号失真。平行铜印制线之间的电感和电容会导致串扰,而大开关电流会导致接地反弹。误码率(BER)将会上升,因为更多比特将被解析为“0”或“1”。

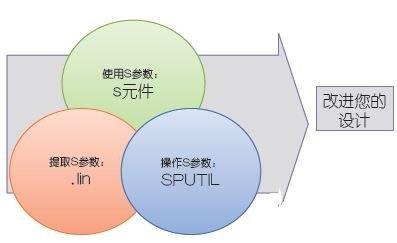

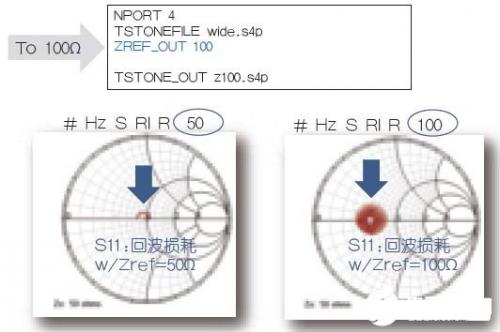

因此,为了确保信号完整性,需要对 PCB 印制线的传输线效应以及封装、连接器和电缆的频率响应进行全面分析。通过减少 PCB 原型设计与测量的大量迭代次数,精准的 PCB 级 SPICE 分析可节省时间和金钱。

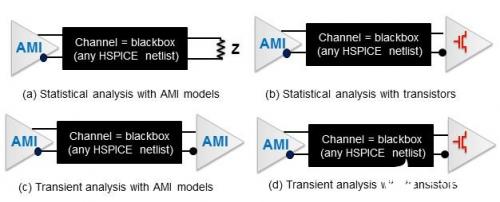

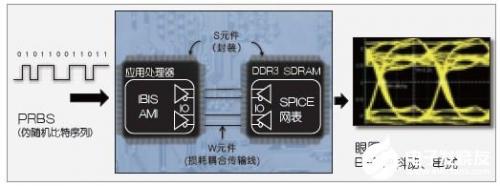

图 1 显示了一个内存接口,它是多千兆芯片间通信的一个典型例子。相同的概念也适用于 USB 3.0、HDMI、多千兆 Ethernet 设备等高速串行 I/O。通信通道由芯片的 I/O 模型、封装、连接器及电缆的散射参数(S 参数)模型以及印制线的损耗耦合传输线模型构成。I/O 模型由芯片厂商提供。简单的 I/O 缓存器可以用 IBIS 模型精确表示。配备有源预加重和均衡功能的更加复杂的 I/O 电路通常采用经过加密的晶体管级 HSPICE 网表的形式,或者采用源于晶体管级表示的 IBIS-AMI 模型。作为晶体管级仿真的黄金参考模型,HSPICE 使用经过晶圆厂认证的晶体管模型提供最为精确的 I/O 电路行为。不仅如此,大多数芯片厂商使用 HSPICE 来验证他们的 IBIS 和 IBIS-AMI 模型。因此,在电路板一级使用 HSPICE 最符合芯片厂商的意图。对于 IBIS-AMI 模型而言,HSPICE 具备独特优势,除了逐比特和统计眼图模式之外,它还能在真正的瞬态模式下模拟这些模型。

图 1:用于信号完整性分析的典型系统配置。

发帖

发帖

回复

回复

楼主

楼主

回复

回复

举报

举报