广州创龙结合TI KeyStone系列多核架构TMS320C665x及Xilinx Artix-7系列FPGA设计的TL665xF-EasyEVM开发板是一款DSP+FPGA高速大数据采集处理平台,其底板采用沉金无铅工艺的6层板设计,适用于高端图像处理、软件无线电、雷达声纳、高端数控系统、机器视觉等高速数据处理领域。核心板在内部通过uPP、EMIF16、SRIO通信接口将DSP与FPGA结合在一起,组成DSP+FPGA架构,实现了需求独特、灵活、功能强大的DSP+FPGA高速数据采集处理系统。

TL665xF-EasyEVM开发板引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。创龙不仅提供丰富的Demo程序,还提供DSP核间通信、DSP与FPGA间通讯开发教程以及全面的技术支持,协助客户进行底板设计和调试以及多核软件开发。

现有创龙年终大促:

●现购买DSP、ARM、FPGA开发板,仿真器(XDS560V2、XDS200、XDS100V2、DLC9LP等)全场第二件半价;

●更有六重好礼免费送:2020年定制日历/保温杯/小米签字笔/魔方插座/U盘/小米移动电源;

→11月15日-12月31日限时抢购,点击:https://tronlong.taobao.com/

JTAG接口

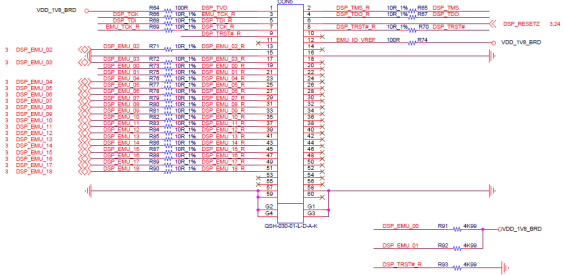

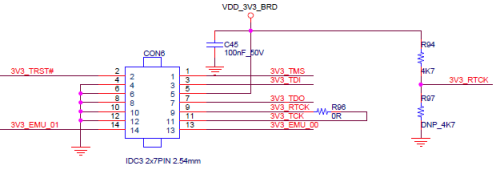

开发板引出3个JTAG接口,DSP端2个(CON5:MIPI、CON6:TI Rev B JTAG),FPGA端1个(CON8:FPGA JTAG),硬件及引脚定义如下图:

串口

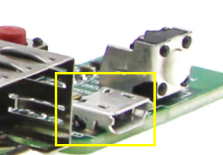

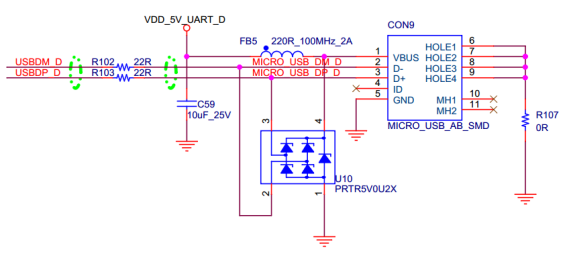

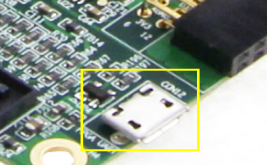

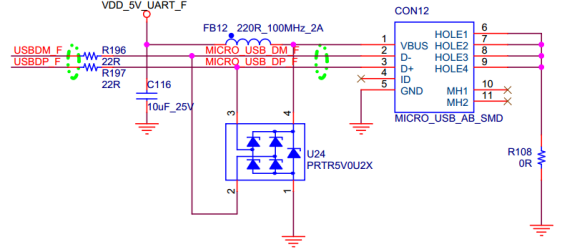

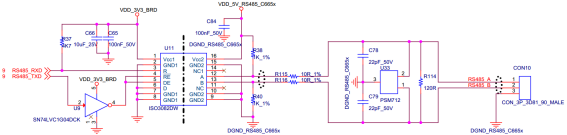

开发板上共引出了3个串口,分别是CON9、CON10和CON12。DSP端2个,CON9是UART0,使用CH340转成Micro USB接口;CON10是UART1,为RS485串口。FPGA端1个,CON12是UART,使用CH340转成Micro USB接口,硬件及引脚定义如下图:

回复

回复

举报

举报

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主