分享到:

TLZ7x-EasyEVM是广州创龙基于Xilinx Zynq-7000 SoC设计的高速数据采集处理开发板,采用核心板+底板的设计方式,尺寸为160mm*108mm,它主要帮助开发者快速评估核心板的性能。

核心板采用12层板沉金无铅设计工艺,尺寸为62mm*38mm,引出PL端和PS端全部可用资源信号引脚,降低了开发难度和周期,以便开发者进行快捷的二次开发使用。

底板采用4层无铅沉金电路板设计,为了方便用户学习开发参考使用,下面引出了各种常见的硬件说明。

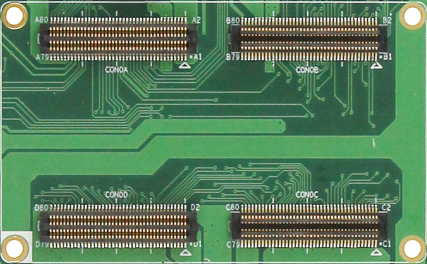

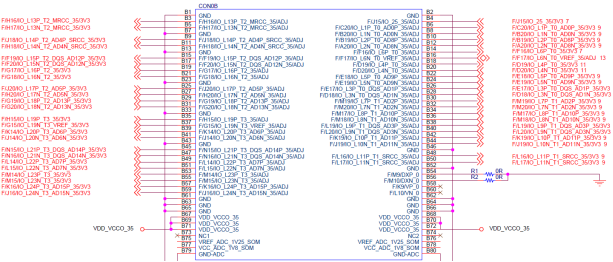

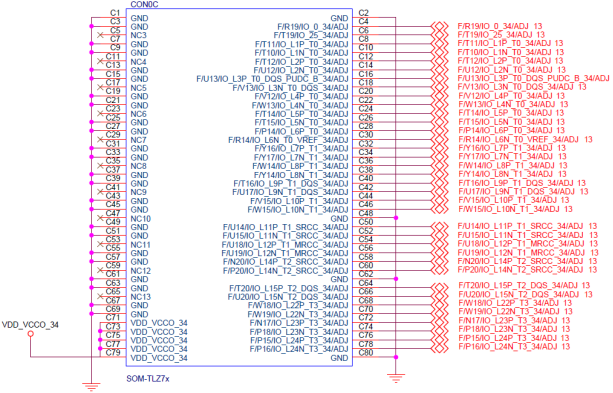

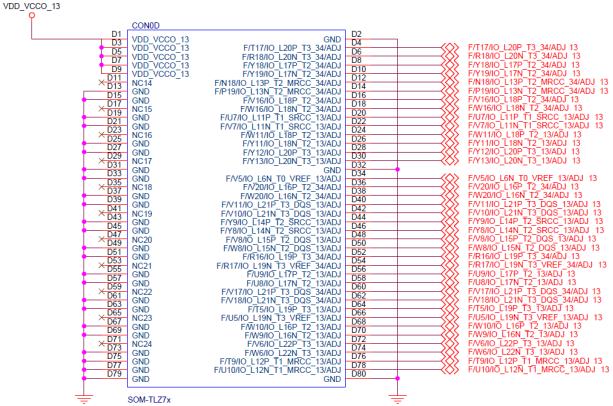

底板B2B连接器

开发板使用底板+核心板设计模式,通过4个80pin、合高4.0mm的B2B连接器对接,其中底板CON0A和CON0D为母座,CON0B和CON0C为公座,以下为底板各个B2B的引脚定义:(数据手册见Datasheet目录)

晶振

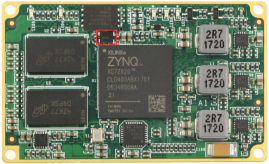

核心板的PS端,晶振为33.3MHz,如下图所示:

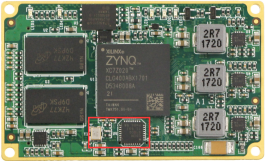

核心板的PL端,晶振为25MHz,配合时钟芯片产生200MHz到CPU Y6/Y7脚与K17/K18脚,如下图所示:(引脚说明见《SOM-TLZ7x核心板引脚说明》)

(0 )

(0 )

回复

回复

举报

举报

发表回复

版

块

导

航

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主