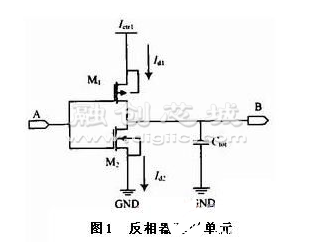

1、VCO延迟单元工作原理

图1所示为电流饥饿型VCO中的单级结构。PNP管M1和NPN管M2是延迟单元的组成部分,Ictrl是用于控制电容的放电电流Id1和充电电流Id2,他们是构成环形振荡器的每一级。Ictrl控制着流过M1管和M2管的电流,所以由M1管和M2管构成的延迟单元处于电流饥饿状态。每一级迟单元处于电流饥饿状态。每一级的电流都由同一个电流源所镜像,所以Id1=Id2同时电流大小由输入控制电流Ictrl控制。

反相延迟主要是2个原因:一个是RC的充电时间;另一个是反相器的预置电压。而这2个延迟时间的产生都是可以通过调整宽长比来实现。环形反相的次数必须是奇数,这样电路才不会锁定导致振荡失败。而差动结构的振荡器级电路数可以是偶数,只要将其中的一级接成不反相的。这种灵活性是差动电路优于单端电路的一个优点。

2、电流饥饿型VCO

如图2所示VCO由11级单端反相延时单元组成的差分电流饥饿型环型振荡器结构,11级差分反相延迟单元,交叉耦合输出结构转为单端输出,其振荡电压可达到全摆幅。交叉耦合、栅极接地的P管,在两个环之间加入一个反相器,使它们的输出信号相位差为180°。为了在上电的时候能立即使两个振荡器同步并保持180°的输出相差,这两个门的尺寸必须设得比较大以便有足够大的驱动能力。这种结构能够有效地抑制环境噪声包括电源和衬底噪声的影响,因此具有良好的抗噪能力。在设计环型振荡器时,应充分考虑每级输入输出点的电容负载,保证每一级的延时都相同,这样每个输入输出点的振荡频率才能相同。

此外,由于沟道长度L决定了最大工作频率,因此在满足最大工作频率指标的条件下应尽可能增加沟道长度以减少电路对工艺参数的敏感程度,即使在最坏情况下仍能保证电路正常工作。第一级反相器的控制电流来自于PLL中RC滤波器的输出电压转换过来的。在设计反相器的宽长比时要保证有足够大的控制电流调节范围,同时也要使沟道长度足够长以消除短沟道效应。反相器MOS管的衬底与滤波器电容接同一个参考地电位,这样可以保证PMOS管和NMOS管不受接地噪声的影响。在与控制支路平行的电流通路中,NMOS管是长沟道管,它为VCO提供小的偏置电流,保证了当控制管工作在亚阈值状态时振荡器仍能振荡。反相器电容管连接在虚地线与VDD之间,其作用等效一个电容,它能有效地限制虚地线的电压波动,从而增强VCO的抗噪声能力。如果需要较大的电容值,可以通过多管并联的方法得到。但是该电路需要设计一个良好的电压/电流转换电路,即控制电压变换电路。

3、控制电压交换电路

控制电压变换电路如图3所示,该电路的工作原理是在保持振荡器控制电流范围不变的情况下对RC滤波器的输出电压,即变换电路的输入电压进行成比例缩放。这样使得振荡控制支路在临界饱和工作状态下能够提供更大的控制电流,从而改善高频区域的线性度,增大VCO的线性覆盖频率范围。在图3中,控制管M1是做阻抗变换,M2,M3用于电压的放大,第一级反相放大管采用PMOS管的形式放大很小的电压,M3管是第二级反相放大NMOS管。这样可以保证输出电压跟输入电压是具有同相功能。该控制电压变换电路的偏置电路采用共源共栅结构,完全适用于低压电路。该结构不仅增强变换电压对电源,工艺,温度依赖性,输出电流噪声的干扰能力,同时抑制了电源噪声对VCO输入电压的影响。 M1,M13,M18管组成了低压共源共栅结构,这时M1管的栅电压为(Vth+2Vds),该电压由M18和M22管组成的偏置支路提供。通过隔离控制管和振荡器控制电流,可以进一步抑制振荡器产生的电压振荡对控制管的影响,降低了控制电流的波动,从而减小了VCO输出的频率抖动,大大降低了VCO输出的相位噪声,有效地提高了VCO输出的频谱纯度。

4、仿真结果

该电路的电源电压为2.5 V,使用Spectre仿真工具,VCO电路得到的输出频率与控制电压特性曲线和相噪特性曲线结果如图4和图5所示。图4为VCO的输出相位噪声曲线,可见低频的1/f噪声得到了很好地抑制。在偏离中心频率600 kHz处的相位噪声为-108 dBc/Hz。图5为VCO的输出频率与控制电压特性曲线表明,VCO的控制电压调节范围是0.6~2.0 V,线性区频率覆盖范围是60~480 MHz,压控增益为300 MHz/V,满足了以太网物理层芯片的时钟频率要求。表1给出了整个VCO的性能参数指标。

5、结语

本文设计了一个适用于以太网物理层芯片时钟同步PLL的高宽带低噪声VCO,采用了具有良好抗噪能力的交叉耦合电流饥饿型差分环形振荡器。仿真结果表明,在同样输入噪声和环境噪声的情况下,本文的VCO中心频率为250MHz时,压控增益线性区频率覆盖范围是60~480MHz,在偏离中心频率600 kHz处的相位噪声为-108 dBc/Hz,较文献中传统的反相器延迟单元的环形VCO性能有明显的改善。说明了改进后的电路具有较宽的频率调节范围,较好的线性度和较低的相位噪声,完全满足以太网物理层芯片时钟同步PLL的性能要求。

回复

回复

举报

举报

块

导

航

举报

请选择举报类别

- 广告垃圾

- 违规内容

- 恶意灌水

- 重复发帖

发帖

发帖

回复

回复

楼主

楼主